- 您現在的位置:買賣IC網 > PDF目錄360867 > INTEL740 64-Bit Graphics (GUI) Accelerator PDF資料下載

參數資料

| 型號: | INTEL740 |

| 英文描述: | 64-Bit Graphics (GUI) Accelerator |

| 中文描述: | 64位圖形(GUI)的加速器 |

| 文件頁數: | 10/41頁 |

| 文件大?。?/td> | 435K |

| 代理商: | INTEL740 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁

Intel387

TM

DX MATH COPROCESSOR

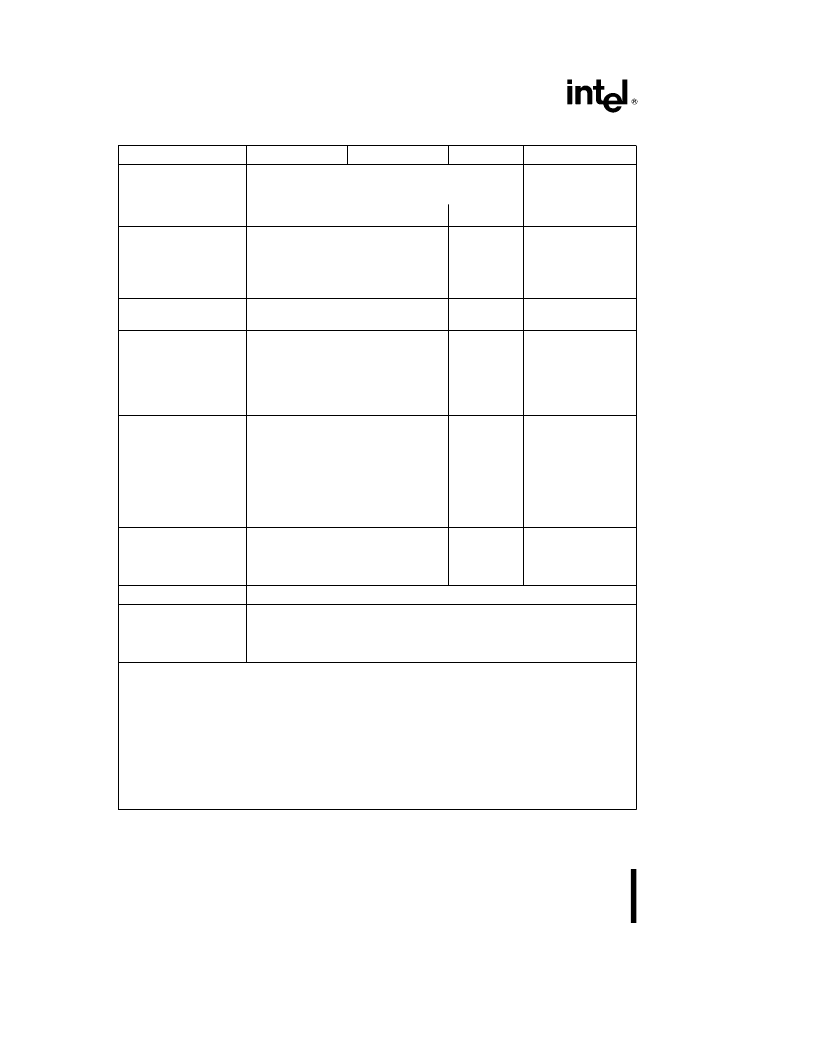

Table 2.2. Condition Code Interpretation

Instruction

C0 (S)

C3 (Z)

C1 (A)

C2 (C)

FPREM, FPREM1

(see Table 2.3)

Three least significant bits

of quotient

Reduction

0

e

complete

1

e

incomplete

Q2

Q0

Q1

or O/U

Y

FCOM, FCOMP,

FCOMPP, FTST,

FUCOM, FUCOMP,

FUCOMPP, FICOM,

FICOMP

Result of comparison

(see Table 2.4)

Zero

or O/U

Y

Operand is not

comparable

(Table 2.4)

FXAM

Operand class

(see Table 2.5)

Sign

Operand class

(Table 2.5)

or O/U

Y

FCHS, FABS, FXCH,

FINCSTP, FDECSTP,

Constant loads,

FXTRACT, FLD,

FILD, FBLD,

FSTP (ext real)

Zero

or O/U

Y

UNDEFINED

UNDEFINED

FIST, FBSTP,

FRNDINT, FST,

FSTP, FADD, FMUL,

FDIV, FDIVR,

FSUB, FSUBR,

FSCALE, FSQRT,

FPATAN, F2XM1,

FYL2X, FYL2XP1

Roundup

or O/U

Y

UNDEFINED

UNDEFINED

FPTAN, FSIN

FCOS, FSINCOS

Roundup

or O/U

Y

,

undefined

if C2

e

1

Reduction

0

e

complete

1

e

incomplete

UNDEFINED

FLDENV, FRSTOR

Each bit loaded from memory

FLDCW, FSTENV,

FSTCW, FSTSW,

FCLEX, FINIT,

FSAVE

UNDEFINED

O/U

Y

When both IE and SF bits of status word are set, indicating a stack exception, this bit

distinguishes between stack overflow (C1

e

1) and underflow (C1

e

0).

If FPREM or FPREM1 produces a remainder that is less than the modulus, reduction is

complete. When reduction is incomplete the value at the top of the stack is a partial

remainder, which can be used as input to further reduction. For FPTAN, FSIN, FCOS, and

FSINCOS, the reduction bit is set if the operand at the top of the stack is too large. In this

case the original operand remains at the top of the stack.

Reduction

Roundup

When the PE bit of the status word is set, this bit indicates whether the last rounding in the

instruction was upward.

UNDEFINED Do not rely on finding any specific value in these bits.

10

10

相關PDF資料 |

PDF描述 |

|---|---|

| INTRO_TO_TRANSISTOR | |

| INTRUMENT | For EM60000 series |

| IO100VXI | |

| IO110VXI | |

| IO120VXI | |

相關代理商/技術參數 |

參數描述 |

|---|---|

| INTEL82801 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:82801AB (ICH0) I/O Controller Hub |

| INTEL82802AB | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Firmware Hub (FWH) |

| INTELLIGENT CHARGER + 4AA | 制造商:Energizer 功能描述:Bulk |

| INTELLI-INCH-LR-STARTER K | 制造商:ALL MOTION 功能描述:Intelli-Inch Stepper & Controller Starter Kit |

| INTELLIPANEL | 制造商:GJD 功能描述:EXTENSION LEAD 8GANG INTELLIPANEL 制造商:GJD 功能描述:EXTENSION LEAD, 8GANG, INTELLIPANEL |

發(fā)布緊急采購,3分鐘左右您將得到回復。