- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄1924 > IDT82P2828BHG (IDT, Integrated Device Technology Inc)IC LIU T1/J1/E1 28+1CH 640-PBGA PDF資料下載

參數(shù)資料

| 型號(hào): | IDT82P2828BHG |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁(yè)數(shù): | 19/154頁(yè) |

| 文件大小: | 0K |

| 描述: | IC LIU T1/J1/E1 28+1CH 640-PBGA |

| 標(biāo)準(zhǔn)包裝: | 5 |

| 類(lèi)型: | 線路接口裝置(LIU) |

| 規(guī)程: | E1 |

| 電源電壓: | 3.13 V ~ 3.47 V |

| 安裝類(lèi)型: | 表面貼裝 |

| 封裝/外殼: | 640-BGA 裸露焊盤(pán) |

| 供應(yīng)商設(shè)備封裝: | 640-PBGA-EP(31x31) |

| 包裝: | 托盤(pán) |

| 其它名稱(chēng): | 82P2828BHG |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)當(dāng)前第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)

IDT82P2828

28(+1) CHANNEL HIGH-DENSITY T1/E1/J1 LINE INTERFACE UNIT

Programming Information

115

February 6, 2009

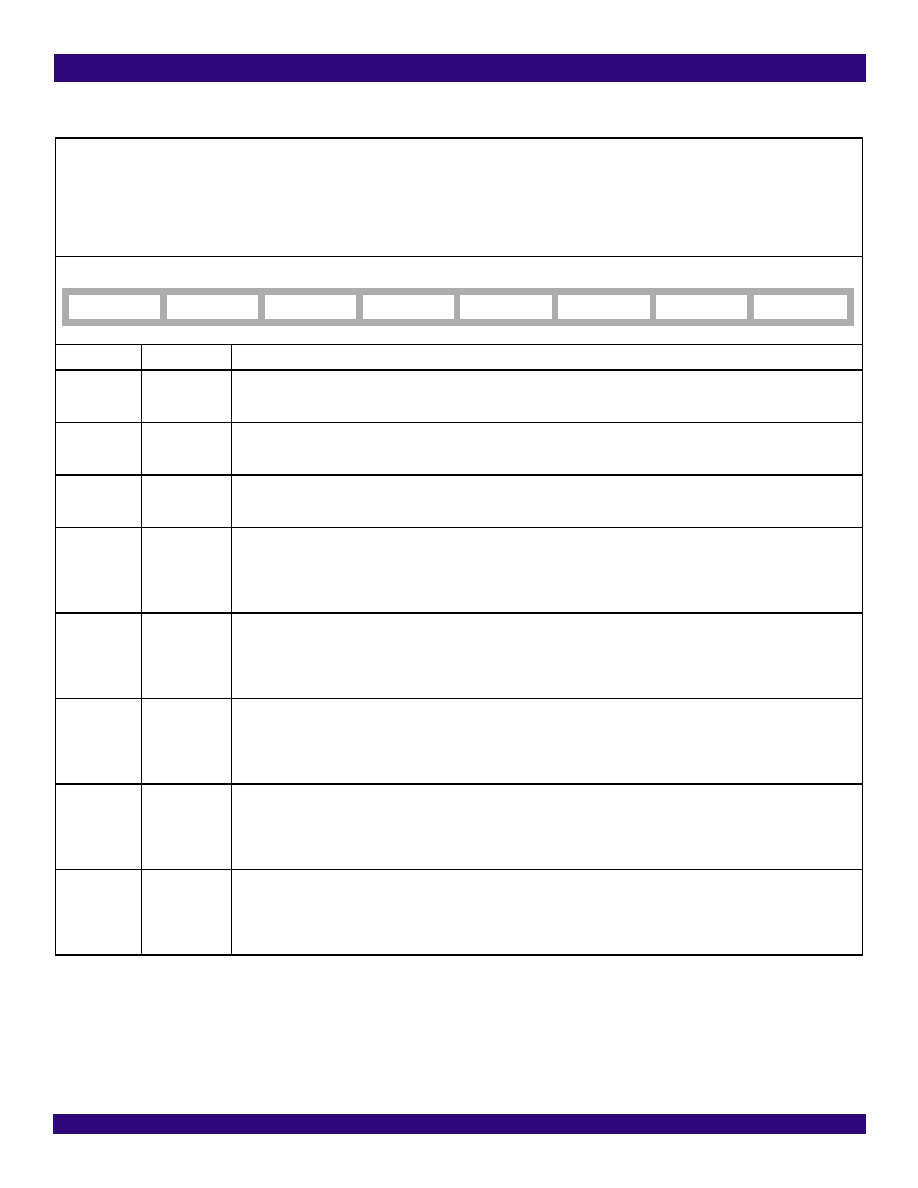

INTS0 - Interrupt Status Register 0

Address: 020H, 060H, 0A0H, 0E0H, 120H, 160H, 1A0H, 1E0H, (CH1~CH8)

220H, 260H, 2A0H, 2E0H, 320H, 360H, 3A0H, 3E0H, (CH9~CH16)

420H, 460H, 4A0H, 4E0H, 520H, 560H, 5A0H, 5E0H, (CH17~CH24)

620H, 660H, 6A0H, 6E0H, (CH25~CH28)

7E0H (CH0)

Type: Read / Write

Default Value: 00H

Bit

Name

Description

7

DAC_IS

This bit indicates the interrupt status of the waveform amplitude overflow.

0: No waveform amplitude overflow interrupt is generated; or a ‘1’ is written to this bit. (default)

1: Waveform amplitude overflow interrupt is generated and is reported by the INT pin.

6

TJA_IS

This bit indicates the interrupt status of the TJA FIFO overflow or underflow.

0: No TJA FIFO overflow or underflow interrupt is generated; or a ‘1’ is written to this bit. (default)

1: TJA FIFO overflow or underflow interrupt is generated and is reported by the INT pin.

5

RJA_IS

This bit indicates the interrupt status of the RJA FIFO overflow or underflow.

0: No RJA FIFO overflow or underflow interrupt is generated; or a ‘1’ is written to this bit. (default)

1: RJA FIFO overflow or underflow interrupt is generated and is reported by the INT pin.

4

TOC_IS

This bit indicates the interrupt status of the Line Driver TOC.

0: No TOC interrupt is generated; or a ‘1’ is written to this bit. (default)

1: TOC interrupt is generated and is reported by the INT pin. When the TOC_IES bit (b4, INTES,...) is ‘0’, a transition from ‘0’ to

‘1’ on the TOC_S bit (b4, STAT0,...) set this bit to ‘1’; when the TOC_IES bit (b4, INTES,...) is ‘1’, any transition (from ‘0’ to ‘1’ or

from ‘1’ to ‘0’) on the TOC_S bit (b4, STAT0,...) set this bit to ‘1’.

3

TCKLOS_IS

This bit indicates the interrupt status of the TCLKn missing.

0: No TCLKn missing interrupt is generated; or a ‘1’ is written to this bit. (default)

1: TCLKn missing interrupt is generated and is reported by the INT pin. When the TCKLOS_IES bit (b3, INTES,...) is ‘0’, a transi-

tion from ‘0’ to ‘1’ on the TCKLOS_S bit (b3, STAT0,...) set this bit to ‘1’; when the TCKLOS_IES bit (b3, INTES,...) is ‘1’, any tran-

sition (from ‘0’ to ‘1’ or from ‘1’ to ‘0’) on the TCKLOS_S bit (b3, STAT0,...) set this bit to ‘1’.

2

TLOS_IS

This bit indicates the interrupt status of TLOS.

0: No TLOS interrupt is generated; or a ‘1’ is written to this bit. (default)

1: TLOS interrupt is generated and is reported by the INT pin. When the TLOS_IES bit (b2, INTES,...) is ‘0’, a transition from ‘0’

to ‘1’ on the TLOS_S bit (b2, STAT0,...) set this bit to ‘1’; when the TLOS_IES bit (b2, INTES,...) is ‘1’, any transition (from ‘0’ to

‘1’ or from ‘1’ to ‘0’) on the TLOS_S bit (b2, STAT0,...) set this bit to ‘1’.

1

SLOS_IS

This bit indicates the interrupt status of the SLOS.

0: No SLOS interrupt is generated; or a ‘1’ is written to this bit. (default)

1: SLOS interrupt is generated and is reported by the INT pin. When the LOS_IES bit (b1, INTES,...) is ‘0’, a transition from ‘0’ to

‘1’ on the SLOS_S bit (b1, STAT0,...) set this bit to ‘1’; when the LOS_IES bit (b1, INTES,...) is ‘1’, any transition (from ‘0’ to ‘1’ or

from ‘1’ to ‘0’) on the SLOS_S bit (b1, STAT0,...) set this bit to ‘1’.

0

LLOS_IS

This bit indicates the interrupt status of the LLOS.

0: No LLOS interrupt is generated; or a ‘1’ is written to this bit. (default)

1: LLOS interrupt is generated and is reported by the INT pin. When the LOS_IES bit (b1, INTES,...) is ‘0’, a transition from ‘0’ to

‘1’ on the LLOS_S bit (b0, STAT0,...) set this bit to ‘1’; when the LOS_IES bit (b1, INTES,...) is ‘1’, any transition (from ‘0’ to ‘1’ or

from ‘1’ to ‘0’) on the LLOS_S bit (b0, STAT0,...) set this bit to ‘1’.

7

654

321

0

DAC_IS

TJA_IS

RJA_IS

TOC_IS

TCKLOS_IS

TLOS_IS

SLOS_IS

LLOS_IS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT82P2916BFG | IC LIU T1/E1/J1 16CH SH 484BGA |

| IDT82P5088BBG | IC LIU T1/E1/J1 OCTAL 256PBGA |

| IDT82V2041EPPG | IC LIU T1/J1/E1 1CH 44-TQFP |

| IDT82V2042EPFG | IC LIU T1/J1/E1 2CH SHORT 80TQFP |

| IDT82V2044EPFG | IC LIU T1/E1 QUAD SHORT 128-TQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT82P2916 | 制造商:IDT 制造商全稱(chēng):Integrated Device Technology 功能描述:16-Channel High-Density T1/E1/J1 Line Interface Unit |

| IDT82P2916BFG | 功能描述:IC LIU T1/E1/J1 16CH SH 484BGA RoHS:是 類(lèi)別:集成電路 (IC) >> 接口 - 電信 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS 產(chǎn)品變化通告:Product Discontinuation 06/Feb/2012 標(biāo)準(zhǔn)包裝:750 系列:* |

| IDT82P2916BFG8 | 制造商:Integrated Device Technology Inc 功能描述:IC LIU T1/E1/J1 16CH SH 484BGA |

| IDT82P5088 | 制造商:IDT 制造商全稱(chēng):Integrated Device Technology 功能描述:Universal Octal T1/E1/J1 LIU with Integrated Clock Adapter |

| IDT82P5088BBBLANK | 制造商:IDT 制造商全稱(chēng):Integrated Device Technology 功能描述:Universal Octal T1/E1/J1 LIU with Integrated Clock Adapter |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。