- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67710 > ICSS98UAE877AHLFIT (INTEGRATED DEVICE TECHNOLOGY INC) 98UAE SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 PDF資料下載

參數(shù)資料

| 型號: | ICSS98UAE877AHLFIT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 98UAE SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

| 封裝: | LEAD FREE, MO-205/MO-255, VFBGA-52 |

| 文件頁數(shù): | 8/18頁 |

| 文件大?。?/td> | 331K |

| 代理商: | ICSS98UAE877AHLFIT |

ICS98UAE877A

1.5V LOW-POWER WIDE-RANGE FREQUENCY CLOCK DRIVER

COMMERCIAL TEMPERATURE GRADE

1.5V LOW-POWER WIDE-RANGE FREQUENCY CLOCK DRIVER

16

ICS98UAE877A

7181/2

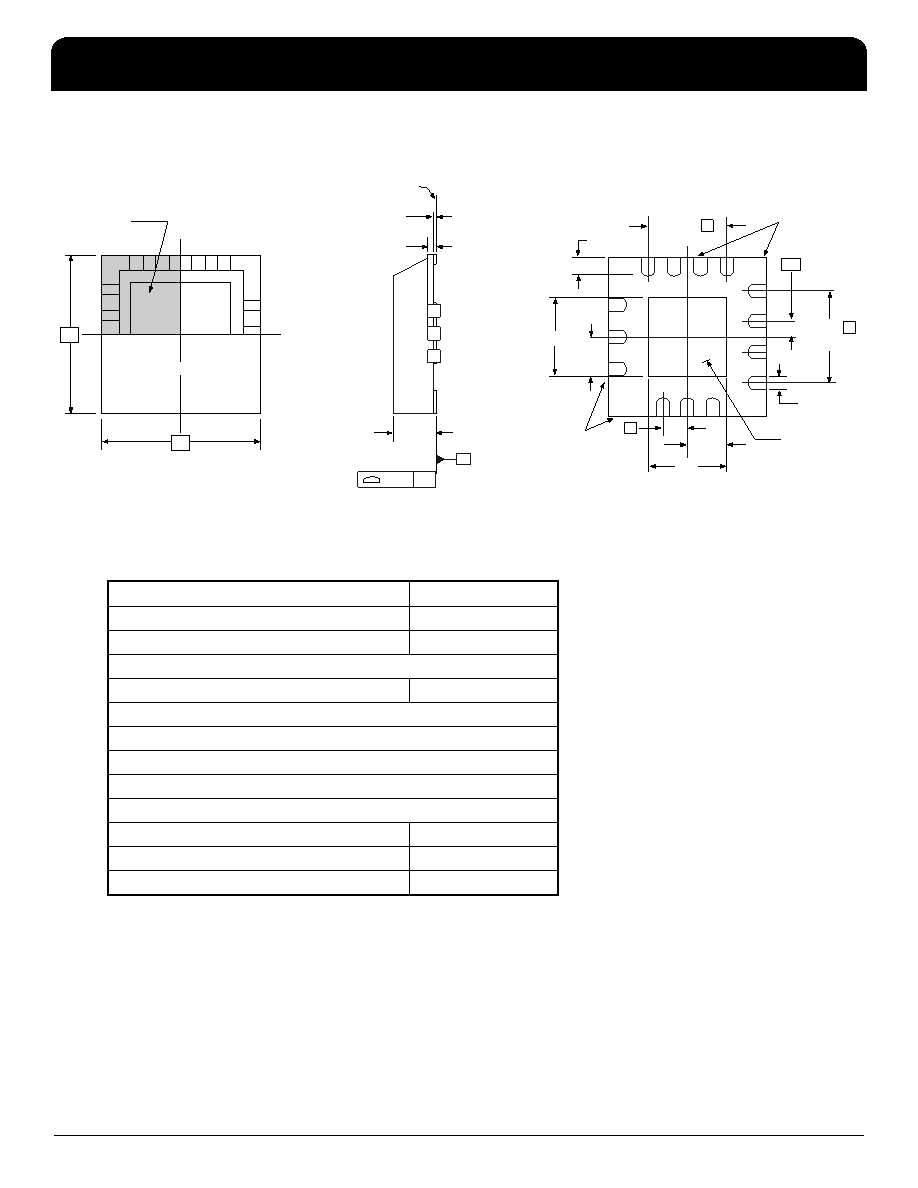

Package Outline and Package Dimensions - MLF

Package dimensions are kept current with JEDEC Publication No. 95

Thermally Enhanced, Very Thin, Fine Pitch Quad Flat / No Lead Plastic Package

Symbol

Min.

Max.

A

0.80

1.00

A1

0

0.05

A3

0.25 Reference

b

0.18

0.30

e

0.50 BASIC

N40

Nd

10

Ne

10

D x E BASIC

6.00 x 6.00

D2

2.75

3.05

E2

2.75

3.05

L

0.30

0.5

C

0.08

C

Seating Plane

A1

A3

A

Anvil

Singulation

or

Sawn

Singulation

N

1

2

Index Area

E

D

Top View

L

E2

E2/2

(ND -1) x e

(Ref.)

ND &NE

Even

(Ref.)

If ND &NE

are Even

(Typ.)

e/2

1

2

b

(NE -1) x e

(Ref.)

Thermal

Base

ND &NE

Odd

(Ref.)

e

D2/2

D2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICSS98UAE877AKLFT | 98UAE SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC40 |

| ICSSSTU3286AHLFT | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| ICSSSTUA32864BHMLFT | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| ICSSSTUA32866BHLFT | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| ICSSSTUA32866BHLFT | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICSSSTU32864 | 制造商:ICS 制造商全稱:ICS 功能描述:25-Bit Configurable Registered Buffer |

| ICSSSTUA32S869B | 制造商:ICS 制造商全稱:ICS 功能描述:14-Bit Configurable Registered Buffer for DDR2 |

| ICSSSTUAF32865A | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 |

| ICSSSTUAF32865AHLFT | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 |

| ICSSSTUAF32866B | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。