- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67710 > ICSS98UAE877AHLFIT (INTEGRATED DEVICE TECHNOLOGY INC) 98UAE SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 PDF資料下載

參數(shù)資料

| 型號: | ICSS98UAE877AHLFIT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 98UAE SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

| 封裝: | LEAD FREE, MO-205/MO-255, VFBGA-52 |

| 文件頁數(shù): | 18/18頁 |

| 文件大?。?/td> | 331K |

| 代理商: | ICSS98UAE877AHLFIT |

ICS98UAE877A

1.5V LOW-POWER WIDE-RANGE FREQUENCY CLOCK DRIVER

COMMERCIAL TEMPERATURE GRADE

1.5V LOW-POWER WIDE-RANGE FREQUENCY CLOCK DRIVER

9

ICS98UAE877A

7181/2

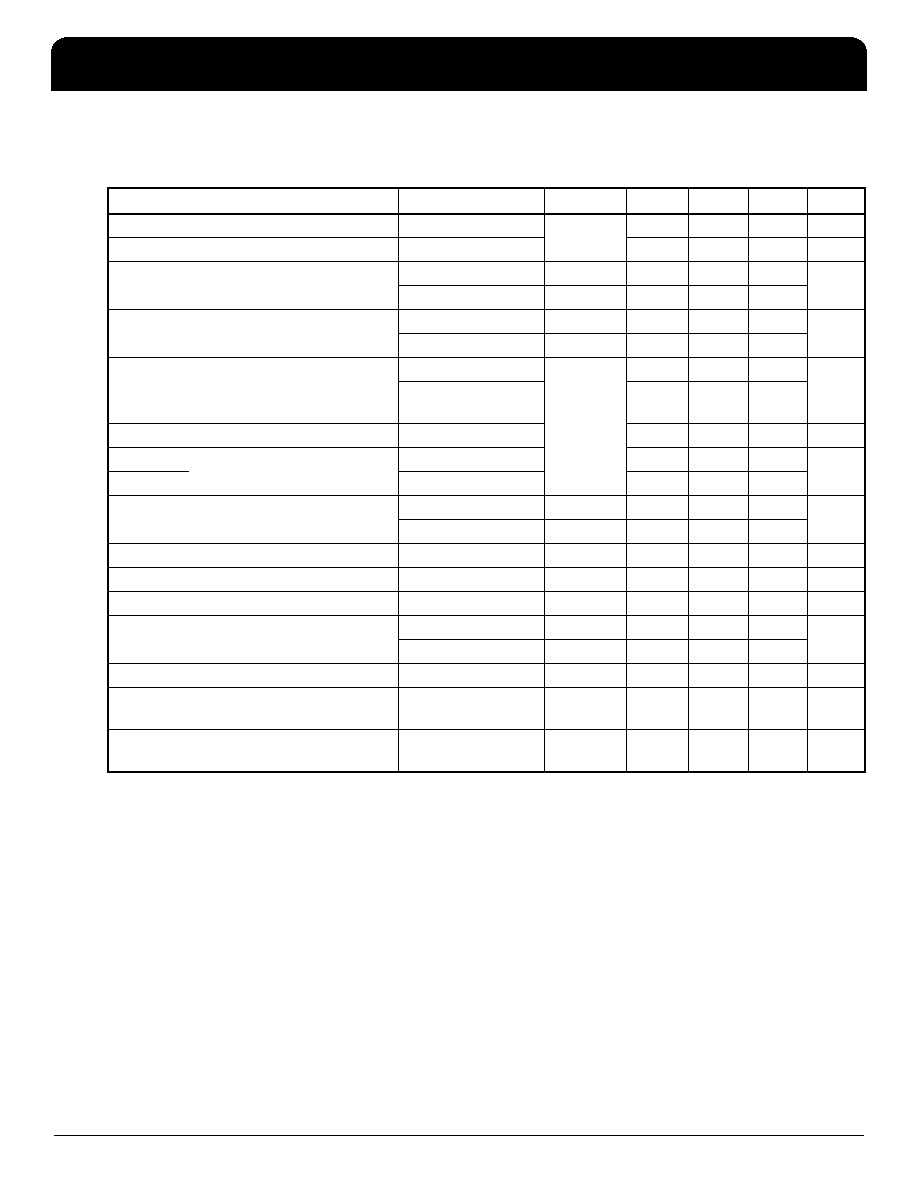

Switching Characteristics Over Recommended Free Air Operating Range

Following Conditions Apply Unless Otherwise Specified:

Commercial: TA = 0°C to +70°C, Industrial: TA = -40°C to +85°C; Supply Voltage AVDD/VDDQ = 1.5V ± 0.075V

Symbol

Parameter1

1

Guaranteed for application frequency range.

Conditions

(MHz)

Min.

Typ.

Max.

Units

tEN

Output Enable Time

OE to any output

160 - 410

4.73

8

ns

tDIS

Output Disable Time

OE to any output

5.82

8

ns

tJIT(PER)

Period Jitter

160 - 270

-40

40

ps

271 - 410

-30

30

tJIT(HPER)

Half-Period Jitter

160 - 270

-60

60

ps

271 - 410

-50

50

SL

r

1(i)

Input Slew Rate

Input Clock

160 - 410

12.5

4

v/ns

Output Enable

(OE, OS)

0.5

SL

r

1(o)

Output Clock Slew Rate

0.8

2

v/ns

tJIT(CC+)

Cycle-to-Cycle Period Jitter

040

ps

tJIT(CC-)

0-40

t()DYN

Dynamic Phase Offset

160 - 270

-50

50

ps

271 - 410

-20

20

tSPO2

2

Static phase offset shifted by design.

Static Phase Offset

271 - 410

-60

0

60

ps

∑(su)

tJIT(PER) + t()DYN + tSKEW(O)80

ps

∑t(h)

t()DYN + tSKEW(O)60

ps

tSKEW

Output-to-Output Skew

160 - 270

60

ps

271 - 410

30

SSC Modulation Frequency

30

33

KHz

SSC Clock Input Frequency

Deviation

0-0.5

%

PLL Loop Bandwidth (-3dB

from unity gain)

2MHz

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICSS98UAE877AKLFT | 98UAE SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC40 |

| ICSSSTU3286AHLFT | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| ICSSSTUA32864BHMLFT | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| ICSSSTUA32866BHLFT | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| ICSSSTUA32866BHLFT | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICSSSTU32864 | 制造商:ICS 制造商全稱:ICS 功能描述:25-Bit Configurable Registered Buffer |

| ICSSSTUA32S869B | 制造商:ICS 制造商全稱:ICS 功能描述:14-Bit Configurable Registered Buffer for DDR2 |

| ICSSSTUAF32865A | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 |

| ICSSSTUAF32865AHLFT | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 |

| ICSSSTUAF32866B | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。