- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67681 > IBM25405GP-3BA200C2 RISC PROCESSOR, PBGA456 PDF資料下載

參數(shù)資料

| 型號: | IBM25405GP-3BA200C2 |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | RISC PROCESSOR, PBGA456 |

| 封裝: | PLASTIC, BGA-456 |

| 文件頁數(shù): | 18/48頁 |

| 文件大小: | 649K |

| 代理商: | IBM25405GP-3BA200C2 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

PowerPC 405GP Embedded Controller

Advance Information

Data Sheet

galdsh5f

06/15/99 Preliminary

IBM Corporation. All rights reserved.

Use is further subject to the provisions at the end of this document.

Page 25 of 48

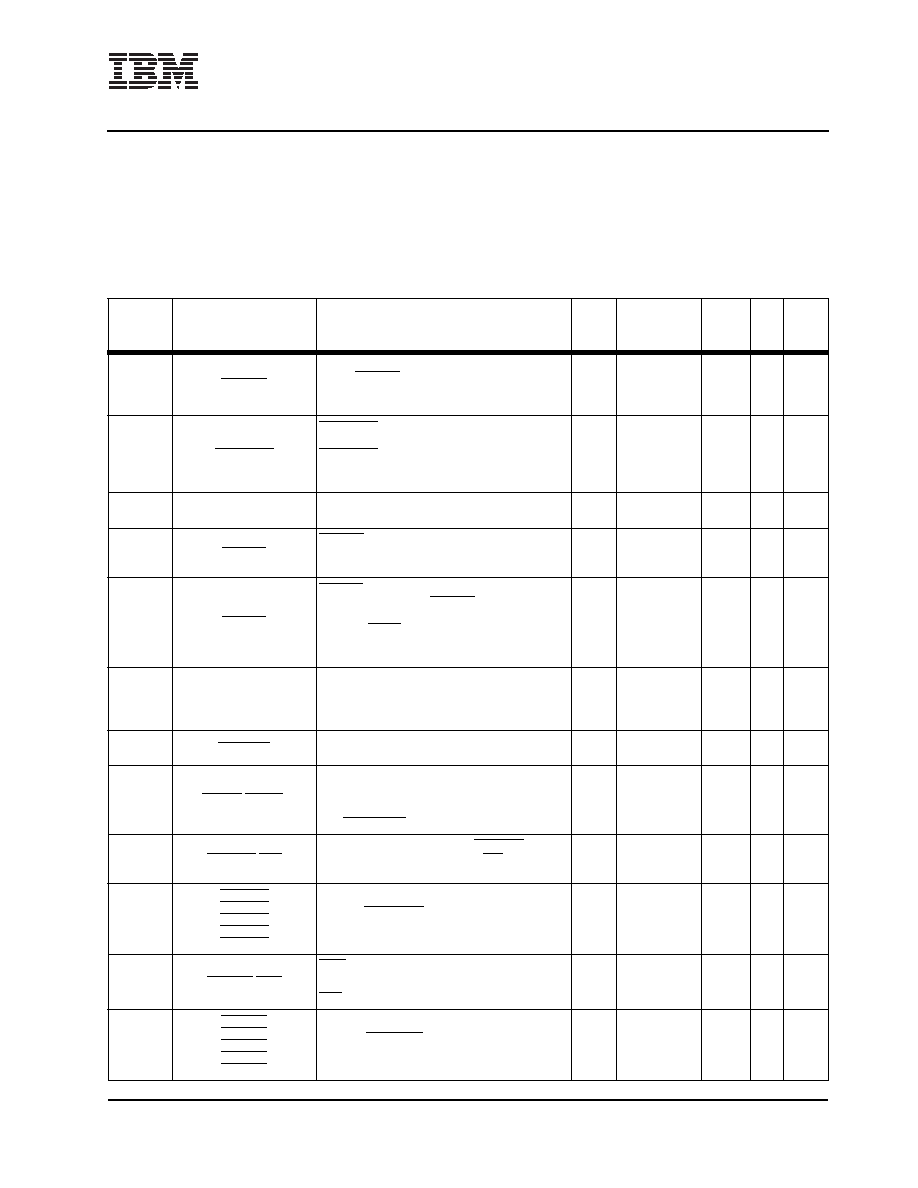

H23

PCIStop

The target of the current PCI transaction may

assert PCIStop to indicate to the requesting

PCI master that it wants to end the current

transaction.

I/O

5V tolerant

3.3V PCI

B4

H25

PCIDevSel

PCIDevSel is driven by the target of the current

PCI transaction. A PCI target asserts

PCIDevSel when it has decoded an address

and command encoding and claims the

transaction.

I/O

5V tolerant

3.3V PCI

B4

P26

PCIIDSel

PCIIDSel is used during configuration cycles to

select the PCI slave interface for configuration

I

5V tolerant

3.3V PCI Rcvr

B4

G24

PCISErr

PCISErr is used for reporting address parity

errors or catastrophic failures detected by a

PCI target.

I/O

5V tolerant

3.3V PCI

B4

G25

PCIPErr

PCIPErr is used for reporting data parity errors

on PCI transactions. PCIPErr is driven active

by the device receiving PCIAD0:31,

PCIC0:3[BE0:3], and PCIParity, two PCI

clocks following the data in which bad parity is

detected.

I/O

5V tolerant

3.3V PCI

B4

B20

PCIClk

PCIClk is used as the asynchronous PCI clock

when in asynch mode. It is unused when the

PCI interface is operated synchronously with

the PLB bus.

I

5V tolerant

3.3V PCI Rcvr

B5

B24

PCIReset

PCI specific reset

O

5V tolerant

3.3V PCI

B

C23

PCIINT[PerWE]

PCI interrupt

or

Peripheral write enable. Logical AND of the

four PerWBE0:3 write byte enables

O

5V tolerant

3.3V PCI

B

C19

PCIReq0[Gnt]

Multipurpose signal, used as PCIReq0 when

internal arbiter is used, and as Gnt when

external arbiter is used.

I

5V tolerant

3.3V PCI Rcvr

B4

C21

B19

A24

G23

J25

PCIReq1

PCIReq2

PCIReq3

PCIReq4

PCIReq5

used as PCIReq1:5 input when internal arbiter

is used

I

5V tolerant

3.3V PCI Rcvr

B4

U23

PCIGnt0[Req]

Gnt0 when internal arbiter is used

or

Req when external arbiter is used

O

5V tolerant

3.3V PCI

B

T23

F23

H26

N23

M24

PCIGnt1

PCIGnt2

PCIGnt3

PCIGnt4

PCIGnt5

Used as PCIGnt1:5 output when internal

arbiter is used.

O

5V tolerant

3.3V PCI

B

Pin Functional Description 35mm, 456-Ball Enhanced Plastic Ball Grid Array Package (Part 2 of 14)

Multiplexed signals are shown in brackets following the first signal name assigned to each multiplexed ball.

Notes:

1. Receiver input has hysteresis

2. Must pull up (recommended value is 3k

to 3.3V, 10k to 5V)

3. Must pull down (recommended value is 1k

)

4. If not used, must pull up (recommended value is 3k

to 3.3V)

5. If not used, must pull down (recommended value is 1k

)

6. Strapping input, pull-up or pull-down required

Ball

Signal Name

Description

I/O

Type

Imped

ance

(

)

BHC

Notes

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IBM25EMPPC603EFG-100 | 32-BIT, 100 MHz, RISC PROCESSOR, PQFP240 |

| IBM25EMPPC603EBG-100 | 32-BIT, 100 MHz, RISC PROCESSOR, CBGA255 |

| IBM25EMPPC740LDBC4000 | 32-BIT, 400 MHz, RISC PROCESSOR, CBGA255 |

| IBM25EMPPC750LCBF3330 | 32-BIT, 333 MHz, RISC PROCESSOR, CBGA360 |

| IBM25EMPPC740LFBF4000 | 32-BIT, 400 MHz, RISC PROCESSOR, CBGA255 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IBM25C710AB3A100 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Controller Miscellaneous - Datasheet Reference |

| IBM25CPC700BB3B66 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral (Multifunction) Controller |

| IBM25CPC700BB3B83 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral (Multifunction) Controller |

| IBM25CPC700CB3A83 | 制造商:IBM 功能描述: |

| IBM25CPC700CB3B66 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral (Multifunction) Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。