- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄224000 > HYS64T16000HDL-2.5-A (INFINEON TECHNOLOGIES AG) 16M X 64 DDR DRAM MODULE, 0.4 ns, DMA200 PDF資料下載

參數(shù)資料

| 型號(hào): | HYS64T16000HDL-2.5-A |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 元件分類(lèi): | DRAM |

| 英文描述: | 16M X 64 DDR DRAM MODULE, 0.4 ns, DMA200 |

| 封裝: | GREEN, SODIMM-200 |

| 文件頁(yè)數(shù): | 19/46頁(yè) |

| 文件大小: | 833K |

| 代理商: | HYS64T16000HDL-2.5-A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)當(dāng)前第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)

HYS64T[16/32/64]0xxxHDL–[2.5/3.7/5]–A

Small Outline DDR2 SDRAM Modules

Electrical Characteristics

Data Sheet

23

Rev. 1.1, 2005-06

02182004-HWZ1-64OM

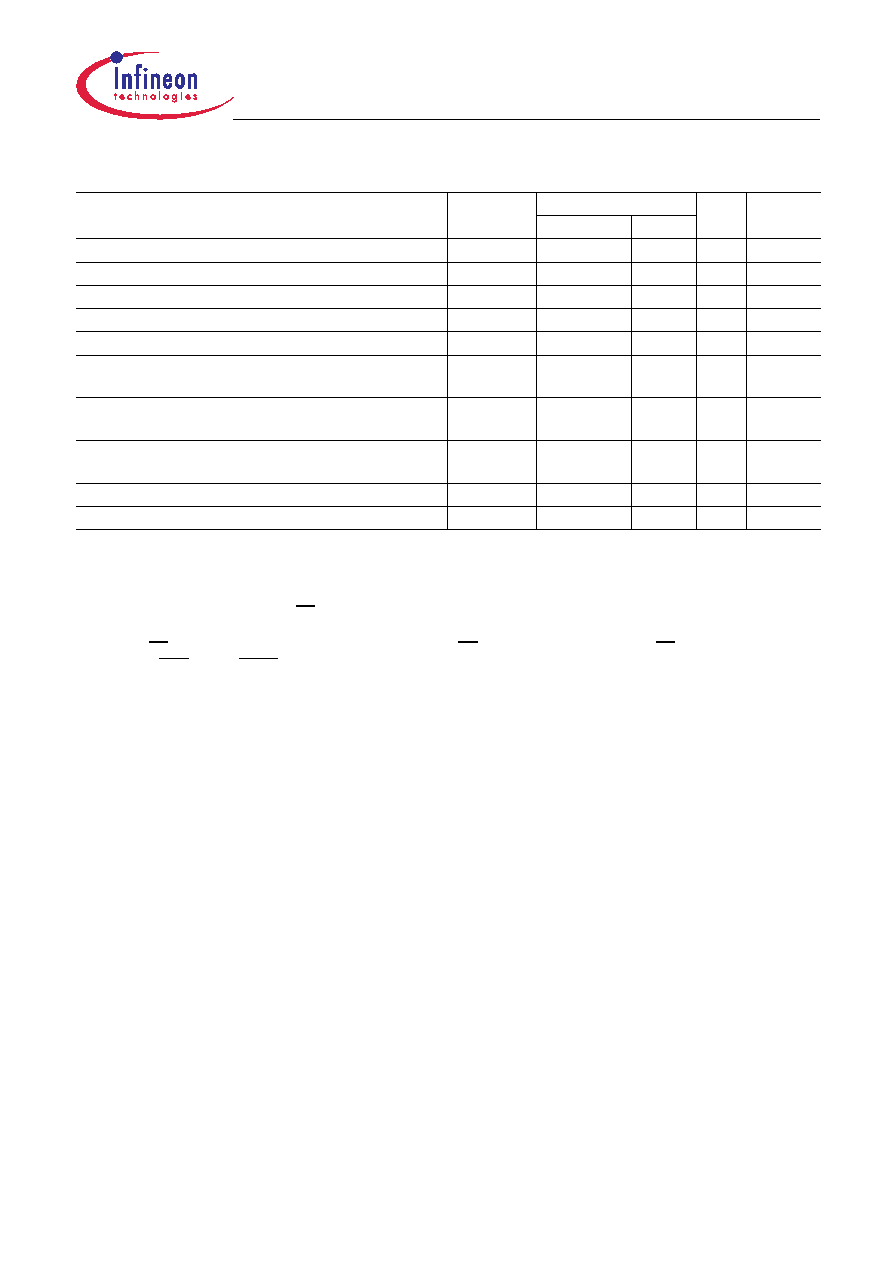

Write preamble

t

WPRE

0.35

—

t

CK

Write postamble

t

WPST

0.40

0.60

t

CK

Write recovery time for write without Auto-Precharge

t

WR

10

—

ns

Write recovery time for write with Auto-Precharge

WR

t

WR/tCK

t

CK

Internal Write to Read command delay

t

WTR

7.5

—

ns

Exit power down to any valid command

(other than NOP or Deselect)

t

XARD

2—

t

CK

Exit active power-down mode to Read command (slow

exit, lower power)

t

XARDS

6 – AL

—

t

CK

Exit precharge power-down to any valid command

(other than NOP or Deselect)

t

XP

2—

t

CK

Exit Self-Refresh to non-Read command

t

XSNR

t

RFC +10

—

ns

Exit Self-Refresh to Read command

t

XSRD

200

—

t

CK

1) For details and notes see the relevant INFINEON component data sheet

2)

V

DDQ = 1.8 V ± 0.1 V; VDD = 1.8 V ± 0.1 V. See notes

4)5)6)7)

3) Timing that is not specified is illegal and after such an event, in order to guarantee proper operation, the DRAM must be

powered down and then restarted through the specified initialization sequence before normal operation can continue.

4) Timings are guaranteed with CK/CK differential Slew Rate of 2.0 V/ns. For DQS signals timings are guaranteed with a

differential Slew Rate of 2.0 V/ns in differential strobe mode and a Slew Rate of 1 V/ns in single ended mode.

5) The CK/CK input reference level (for timing reference to CK/CK) is the point at which CK and CK cross.

The DQS/DQS, RDQS/RDQS, input reference level is the crosspoint when in differential strobe mode

6) Inputs are not recognized as valid until

V

REF stabilizes. During the period before VREF stabilizes, CKE = 0.2 x VDDQ is

recognized as low.

7) The output timing reference voltage level is

V

TT. See Chapter 8 for the reference load for timing measurements.

8) 0

≤ T

CASE ≤ 85 °C

9) 85 °C

< T

CASE ≤ 95 °C

10) x4 & x8

11) x16

Table 16

Timing Parameter by Speed Grade - DDR2-400

Parameter

Symbol

DDR2-400

Unit

Note

1)2)3)4)5)6)7)

Min.

Max.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYS72D64020GR-7-X | 64M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

| HYS72D64020GR-7.5-X | 64M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

| HYS72T128000EU-2.5-C2 | 128M X 72 DDR DRAM MODULE, 0.4 ns, DMA240 |

| HYS72T64000EP-3.7-B2 | 64M X 72 DDR DRAM MODULE, DMA240 |

| HZ20-1 | 19.25 V, 0.5 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE, DO-35 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYS64T16000HU | 制造商:QIMONDA 制造商全稱(chēng):QIMONDA 功能描述:240-Pin Unbuffered DDR2 SDRAM Modules |

| HYS64T16000HU-3.7-A | 制造商:QIMONDA 制造商全稱(chēng):QIMONDA 功能描述:240-Pin Unbuffered DDR2 SDRAM Modules |

| HYS64T16000HU-5-A | 制造商:QIMONDA 制造商全稱(chēng):QIMONDA 功能描述:240-Pin Unbuffered DDR2 SDRAM Modules |

| HYS64T256020EDL | 制造商:QIMONDA 制造商全稱(chēng):QIMONDA 功能描述:200-Pin SO-DIMM DDR2 SDRAM Modules |

| HYS64T256020EDL-2.5-C | 制造商:QIMONDA 制造商全稱(chēng):QIMONDA 功能描述:200-Pin SO-DIMM DDR2 SDRAM Modules |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。