- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370795 > HYE25L256160AF-75 (INFINEON TECHNOLOGIES AG) CAP TANT 10UF 6.3V 20% SMD PDF資料下載

參數(shù)資料

| 型號: | HYE25L256160AF-75 |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | CAP TANT 10UF 6.3V 20% SMD |

| 中文描述: | 片256Mbit移動- RAM的 |

| 文件頁數(shù): | 12/55頁 |

| 文件大小: | 1053K |

| 代理商: | HYE25L256160AF-75 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁

7-0-1-2-3-4-5-6

HYE25L256160AC

256-Mbit Mobile-RAM

Functional Description

Data Sheet

12

V1.1, 2003-04-16

3.2.2

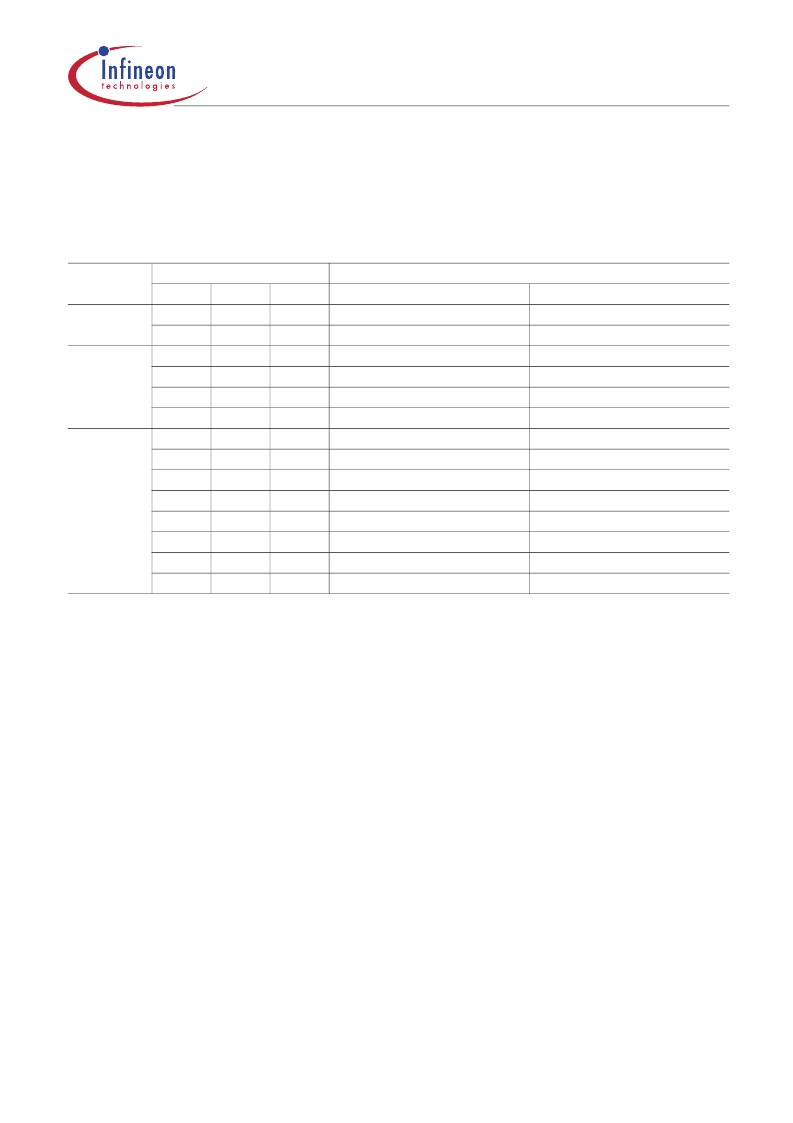

Accesses within a given burst may be programmed to be either sequential or interleaved; this is referred to as the

burst type and is selected via bit A3. The ordering of accesses within a burst is determined by the burst length, the

burst type and the starting column address, as shown in

Table 4

.

Burst Type

Note:

1. For a burst length of two, Ai-A1 selects the two-data-element block; A0 selects the first access within the block.

2. For a burst length of four, Ai-A2 selects the four-data-element block; A1-A0 selects the first access within the

block.

3. For a burst length of eight, Ai-A3 selects the eight-data- element block; A2-A0 selects the first access within

the block.

4. Whenever a boundary of the block is reached within a given sequence above, the following access wraps

within the block.

3.2.3

The Read latency, or CAS latency, is the delay, in clock cycles, between the registration of a Read command and

the availability of the first burst of output data. The latency can be programmed 2 and 3 clocks.

If a Read command is registered at rising clock edge n, and the latency is

m

clocks, the data is available nominally

coincident with rising clock edge

n + m

.

Reserved states should not be used as unknown operation or incompatibility with future versions may result.

Read Latency

3.2.4

The normal operating mode is selected by issuing a Mode Register Set Command with bits A12-A7 set to zero,

and bits A6-A0 set to the desired values. Burst Length for Write bursts is fixed to one by issuing a Mode Register

Set command with bits A12-A10 and A8-A7 each set to zero, bit A9 set to one, and bits A0-A6 set to the desired

values.

All other combinations of values for A12-A7 are reserved for future use and/or test modes. Test modes and

reserved states should not be used as unknown operation or incompatibility with future versions may result.

Operating Mode

Table 4

Burst

Length

Burst Definition

Starting Column Address

A2

A1

Order of Accesses Within a Burst

Type = Sequential

0-1

1-0

0-1-2-3

1-2-3-0

2-3-0-1

3-0-1-2

0-1-2-3-4-5-6-7

1-2-3-4-5-6-7-0

2-3-4-5-6-7-0-1

3-4-5-6-7-0-1-2

4-5-6-7-0-1-2-3

5-6-7-0-1-2-3-4

6-7-0-1-2-3-4-5

A0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Type = Interleaved

0-1

1-0

0-1-2-3

1-0-3-2

2-3-0-1

3-2-1-0

0-1-2-3-4-5-6-7

1-0-3-2-5-4-7-6

2-3-0-1-6-7-4-5

3-2-1-0-7-6-5-4

4-5-6-7-0-1-2-3

5-4-7-6-1-0-3-2

6-7-4-5-2-3-0-1

7-6-5-4-3-2-1-0

2

4

0

0

1

1

0

0

1

1

0

0

1

1

8

0

0

0

0

1

1

1

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYE25L256160AC-7.5 | BJAWBMSpecialty DRAMs Mobile-RAM |

| HYM321000GS-60 | 1M x 32-Bit Dynamic RAM Module 2M x 16-Bit Dynamic RAM Module |

| HYM321000S-60 | 1M x 32-Bit Dynamic RAM Module 2M x 16-Bit Dynamic RAM Module |

| HYM321000S | 1M x 32-Bit Dynamic RAM Module 2M x 16-Bit Dynamic RAM Module |

| HYM321000S-50 | 1M x 32-Bit Dynamic RAM Module 2M x 16-Bit Dynamic RAM Module |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYESD0514P | 制造商:HY 制造商全稱:HY ELECTRONIC CORP. 功能描述:4 Channel Low Capacitance ESD Protection Diode Array |

| HYESD0524A6 | 制造商:HY 制造商全稱:HY ELECTRONIC CORP. 功能描述:4 Channel Low Capacitance ESD Protection Diode Array |

| HYESD0524P | 制造商:HY 制造商全稱:HY ELECTRONIC CORP. 功能描述:4 Channel Low Capacitance ESD Protection Diode Array |

| HYESD1025QG | 制造商:HY 制造商全稱:HY ELECTRONIC CORP. 功能描述:2 Channel Low Capacitance ESD Protection DIode Array |

| HYESD1065M | 制造商:HY 制造商全稱:HY ELECTRONIC CORP. 功能描述:6 Channel Low Capacitance ESD Protection Diode Array |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。