- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370738 > HY29LV400 4M(X8/X16)|3.0V|55|NOR FLASH - 4M PDF資料下載

參數(shù)資料

| 型號: | HY29LV400 |

| 英文描述: | 4M(X8/X16)|3.0V|55|NOR FLASH - 4M |

| 中文描述: | 4分(X8/X16)| 3.0V | 55 | NOR閃存- 4分 |

| 文件頁數(shù): | 15/40頁 |

| 文件大小: | 550K |

| 代理商: | HY29LV400 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

15

Rev. 1.0/Nov. 01

HY29LV400

internally generated erase pulses and verifies cell

erasure within the proper cell margins. The host

system is not required to provide any controls or

timings during these operations.

After the sector erase data cycle (the sixth bus

cycle) of the command sequence is issued, a sec-

tor erase time-out of 50 μs (min), measured from

the rising edge of the final WE# pulse in that bus

cycle, begins. During this time-out window, an ad-

ditional sector erase data cycle, specifying the

sector address of another sector to be erased, may

be written into an internal sector erase buffer. This

buffer may be loaded in any sequence, and the

number of sectors specified may be from one sec-

tor to all sectors. The only restriction is that the

time between these additional data cycles must

be less than 50 μs, otherwise erasure may begin

before the last data cycle is accepted. To ensure

that all data cycles are accepted, it is recom-

mended that host processor interrupts be disabled

during the time that the additional cycles are be-

ing issued and then be re-enabled afterwards.

If all sectors specified for erasing are protected,

the device returns to reading array data after ap-

proximately 100 μs. If at least one specified sec-

tor is not protected, the erase operation erases

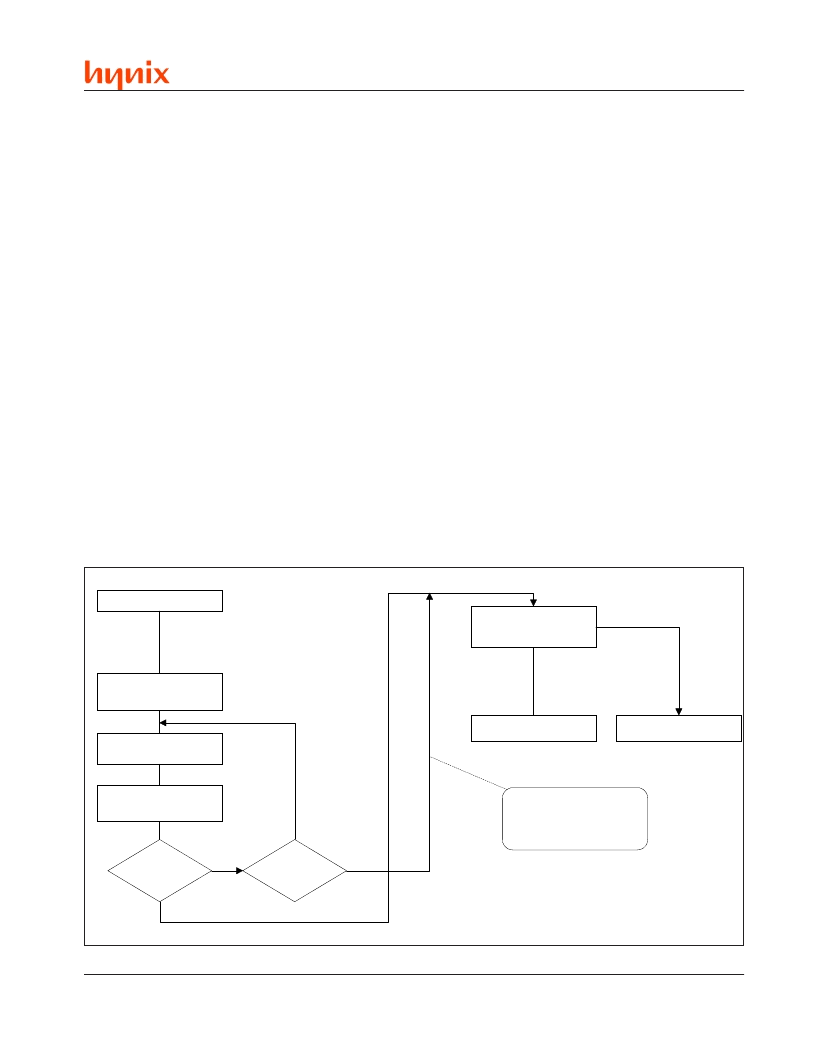

Figure 6. Sector Erase Procedure

the unprotected sectors, and ignores the command

for the sectors that are protected.

The system can monitor DQ[3] to determine if the

50 μs sector erase time-out has expired, as de-

scribed in the Write Operation Status section. If

the time between additional sector erase data

cycles can be insured to be less than the time-

out, the system need not monitor DQ[3].

Any command other than Sector Erase or Erase

Suspend during the time-out period resets the

device to reading array data. The system must

then rewrite the command sequence, including any

additional sector erase data cycles. Once the sec-

tor erase operation itself has begun, only the Erase

Suspend command is valid. All other commands

are ignored.

As for the Chip Erase command, note that a hard-

ware reset immediately terminates the sector

erase operation. To ensure data integrity, the

aborted Sector Erase command sequence should

be reissued once the reset operation is complete.

When the Automatic Erase algorithm terminates,

the device returns to the array Read mode. Sev-

eral methods are provided to allow the host to de-

termine the status of the erase operation, as de-

scribed in the Write Operation Status section.

START

YES

Erase An

Additional Sector

Check Erase Status

(See Write Operation Status

Section)

Setup First (or Next) Sector

Address for Erase Operation

ERASE COMPLETE

Write First Five Cycles of

SECTOR ERASE

Command Sequence

Write Last Cycle (SA/0x30)

of SECTOR ERASE

Command Sequence

Sector Erase

Time-out (DQ[3])

Expired

NO

YES

NO

GO TO

ERROR RECOVERY

DQ[5] Error Exit

Normal Exit

Sectors which require erasure

but which were not specified in

this erase cycle must be erased

later using a new command

sequence

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HY3-9574A-9 | Analog-to-Digital Converter??? 12-Bit |

| HY3-9574B-9 | Analog-to-Digital Converter??? 12-Bit |

| HY3-9574J-5 | Analog-to-Digital Converter??? 12-Bit |

| HY3-9574K-5 | Analog-to-Digital Converter??? 12-Bit |

| HY-9574 | |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HY29LV400BF55 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:4 Mbit (512K x 8/256K x 16) Low Voltage Flash Memory |

| HY29LV400BF55I | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:4 Mbit (512K x 8/256K x 16) Low Voltage Flash Memory |

| HY29LV400BF70 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:4 Mbit (512K x 8/256K x 16) Low Voltage Flash Memory |

| HY29LV400BF70I | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:4 Mbit (512K x 8/256K x 16) Low Voltage Flash Memory |

| HY29LV400BF90 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:4 Mbit (512K x 8/256K x 16) Low Voltage Flash Memory |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。