- 您現(xiàn)在的位置:買賣IC網 > PDF目錄173638 > GS8342D08E-333T (GSI TECHNOLOGY) 4M X 8 STANDARD SRAM, 0.45 ns, PBGA165 PDF資料下載

參數(shù)資料

| 型號: | GS8342D08E-333T |

| 廠商: | GSI TECHNOLOGY |

| 元件分類: | SRAM |

| 英文描述: | 4M X 8 STANDARD SRAM, 0.45 ns, PBGA165 |

| 封裝: | 15 X 17 MM, 1 MM PITCH, FPBGA-165 |

| 文件頁數(shù): | 15/37頁 |

| 文件大?。?/td> | 1668K |

| 代理商: | GS8342D08E-333T |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

Preliminary

GS8342D08/09/18/36E-333/300/250/200/167

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

Rev: 1.02 8/2005

22/37

2003, GSI Technology

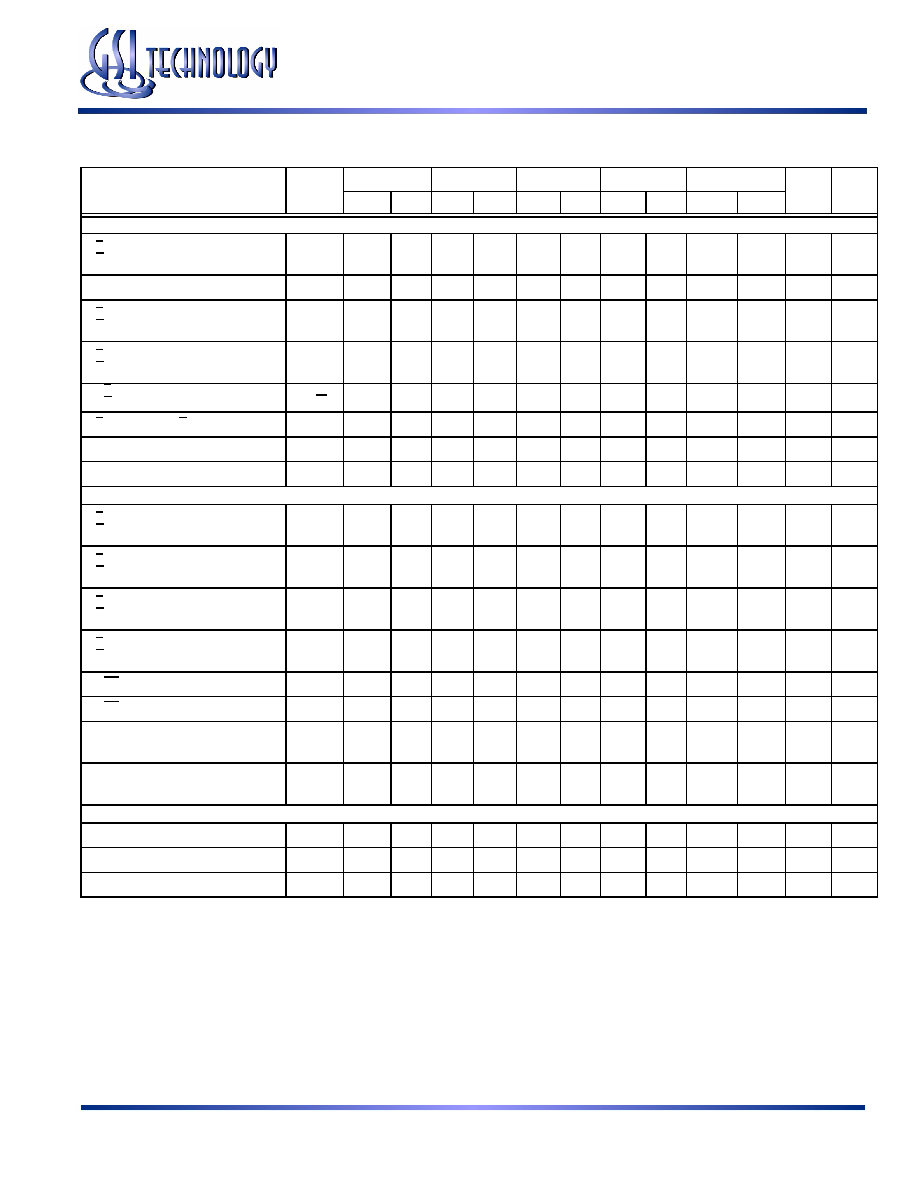

AC Electrical Characteristics

Parameter

Symbol

-333

-300

-250

-200

-167

Units

Notes

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

Clock

K, K Clock Cycle Time

C, C Clock Cycle Time

tKHKH

tCHCH

3.0

3.5

3.3

4.2

4.0

6.3

5.0

7.88

6.0

8.4

ns

tKC Variable

tKCVar

—

0.2

—

0.2

—

0.2

—

0.2

—

0.2

ns

5

K, K Clock High Pulse Width

C, C Clock High Pulse Width

tKHKL

tCHCL

1.2

—

1.32

—

1.6

—

2.0

—

2.4

—

ns

K, K Clock Low Pulse Width

C, C Clock Low Pulse Width

tKLKH

tCLCH

1.2

—

1.32

—

1.6

—

2.0

—

2.4

—

ns

K to K High

C to C High

tKHKH

1.35

—

1.49

—

1.8

—

2.2

—

2.7

—

ns

K, K Clock High to C, C Clock High

tKHCH

0

1.30

0

1.45

0

1.8

0

2.3

0

2.8

ns

DLL Lock Time

tKCLock

1024

—

1024

—

1024

—

1024

—

1024

—

cycle

6

K Static to DLL reset

tKCReset

30

—

30

—

30

—

30

—

30

—

ns

Output Times

K, K Clock High to Data Output Valid

C, C Clock High to Data Output Valid

tKHQV

tCHQV

—

0.45

—

0.45

—

0.45

—

0.45

—

0.5

ns

3

K, K Clock High to Data Output Hold

C, C Clock High to Data Output Hold

tKHQX

tCHQX

–0.45

—

–0.45

—

–0.45

—

–0.45

—

–0.5

—

ns

3

K, K Clock High to Echo Clock Valid

C, C Clock High to Echo Clock Valid

tKHCQV

tCHCQV

—

0.45

—

0.45

—

0.45

—

0.45

—

0.5

ns

K, K Clock High to Echo Clock Hold

C, C Clock High to Echo Clock Hold

tKHCQX

tCHCQX

–0.45

—

–0.45

—

–0.45

—

–0.45

—

–0.5

—

ns

CQ, CQ High Output Valid

tCQHQV

—

0.25

—

0.27

—

0.30

—

0.35

—

0.40

ns

7

CQ, CQ High Output Hold

tCQHQX

–0.25

—

–0.27

—

–0.30

—

–0.35

—

–0.40

—

ns

7

K Clock High to Data Output High-Z

C Clock High to Data Output High-Z

tKHQZ

tCHQZ

—

0.45

—

0.45

—

0.45

—

0.45

—

0.5

ns

3

K Clock High to Data Output Low-Z

C Clock High to Data Output Low-Z

tKHQX1

tCHQX1

–0.45

—

–0.45

—

–0.45

—

–0.45

—

–0.5

—

ns

3

Setup Times

Address Input Setup Time

tAVKH

0.4

—

0.4

—

0.5

—

0.6

—

0.7

—

ns

Control Input Setup Time

tIVKH

0.4

—

0.4

—

0.5

—

0.6

—

0.7

—

ns

2

Data Input Setup Time

tDVKH

0.28

—

0.3

—

0.35

—

0.4

—

0.5

—

ns

相關PDF資料 |

PDF描述 |

|---|---|

| GS8342Q08AE-278 | 4M X 8 DDR SRAM, 0.45 ns, PBGA165 |

| GS84018AB-190 | 256K X 18 CACHE SRAM, 7.5 ns, PBGA119 |

| GS840E18AGT-150T | 256K X 18 CACHE SRAM, 10 ns, PQFP100 |

| GS840E18AT-166IT | 256K X 18 CACHE SRAM, 8.5 ns, PQFP100 |

| GS840F36AGT-10T | 128K X 36 CACHE SRAM, 10 ns, PQFP100 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| GS8342D08GE-400 | 制造商:GSI Technology 功能描述:4M X 8 (36 MEG) SIGMAQUAD II -SEPERATE I/O BURST OF 4 - Trays |

| GS8342D09AE-167 | 制造商:GSI Technology 功能描述:SRAM SYNC DUAL 1.8V 36MBIT 4M X 9 0.5NS 165FPBGA - Trays |

| GS8342D09AE-200 | 制造商:GSI Technology 功能描述:SRAM SYNC DUAL 1.8V 36MBIT 4M X 9 0.45NS 165FPBGA - Trays |

| GS8342D09AE-250 | 制造商:GSI Technology 功能描述:SRAM SYNC DUAL 1.8V 36MBIT 4M X 9 0.45NS 165FPBGA - Trays |

| GS8342D09AE-300 | 制造商:GSI Technology 功能描述:SRAM SYNC DUAL 1.8V 36MBIT 4M X 9 0.45NS 165FPBGA - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復。