- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370311 > GD16367B-52BA ATM Multiplexer PDF資料下載

參數(shù)資料

| 型號: | GD16367B-52BA |

| 英文描述: | ATM Multiplexer |

| 中文描述: | ATM多路復用器 |

| 文件頁數(shù): | 8/14頁 |

| 文件大小: | 122K |

| 代理商: | GD16367B-52BA |

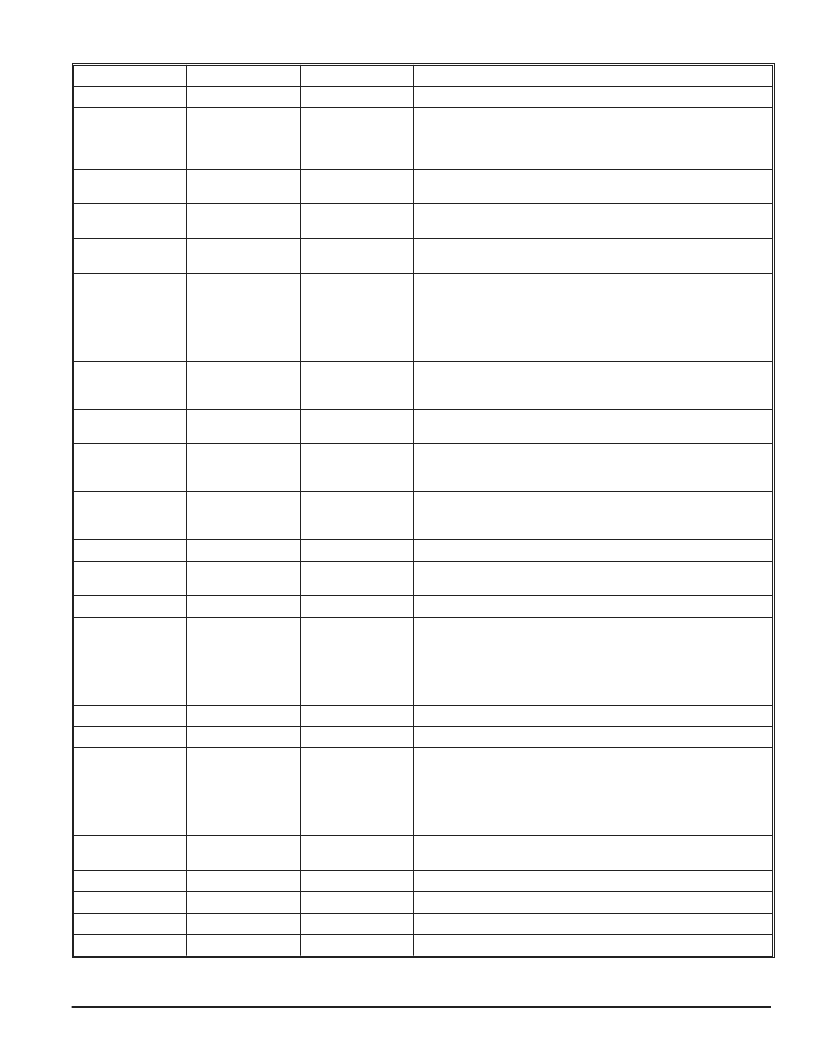

Pin List, GD16368B

Mnemonic:

Pin No.:

Pin Type:

Description:

SIP, SIN

4, 5

LVPECL-IN

Differential serial data input.

DOU0, DOU1,

DOU2, DOU3,

DOU4, DOU5,

DOU6, DOU7

38, 37,

35, 34,

32, 31,

29, 28

CMOS-OUT

2, 4 or 8-bit wide data output. DOU0 is the first received bit, fol-

lowed by DOU1, ....

DOCK

24

CMOS-OUT

70/78, 34/39 or 17/19 MHz clock output selected by PW1 and

PW2.

CODV

25

CMOS-OUT

Code violation output. High for one 70/78 MHz clock period if

error detected, otherwise low. Disabled (low) in NRZ-mode.

SEL1

44

CMOS-IN

When low the CMI decoder is enabled. When high, data is passed

unchanged (NRZ mode).

SEL2, SEL3

43, 42

CMOS-IN

DOUx output phase versus DOCK select:

SEL3

SEL2

0

0

T

DEL

= 0

°

1

1

T

DEL

= 90

°

1

0

T

DEL

= 180

°

0

1

T

DEL

= 270

°

CKRF

41

CMOS-IN

70/78 MHz reference clock input for the CDR block. Used to en-

sure fast acquisition to incoming data and to ensure stable DOCK

output clock in absence of data.

CLOF

48

ANL

Ext. loop filter pin. Connect 1

μ

F in series with 20

from this pin

to the neighbour VEEA pin.

LLSOP, LLSON

19, 20

LVPECL-OUT

Line loop-back serial differential data, 140/155 MHz, CMI or NRZ

according to SEL1. To be connected to LLSIP/LLSIN of the

GD16367B.

LLCOP, LLCON

16, 17

LVPECL-OUT

Line loop-back serial differential clock, 140/155 MHz or 280/311

MHz according to SEL1. To be connected to LLCIP/LLCIN of the

GD16367B.

LLB

18

CMOS-IN

When high, line loop-back is enabled.

SLSIP, SLSIN

8, 7

LVPECL_IN

Switch loop-back serial differential data, 140/155 MHz.

To be connected to SLSOP/SLSON of the GD16367B.

SLB

10

CMOS-IN

When high, switch loop-back is enabled.

PW1, PW2

22, 23

CMOS-IN

Parallel port width / parallel clock rate:

PW1

PW2

0

0

2 bit, DOU0..DOU1 – DOCK = 70/78 MHz

1

0

4 bit, DOU0..DOU3 – DOCK = 35/38 MHz

0

1

8 bit, DOU0..DOU7 – DOCK = 17/19 MHz

1

1

Not valid

TCK

2

ANL-IN

Test clock input, for test purpose only. Connect to VEE.

SELTCK

52

ANL-IN

Test clock select, for test purpose only. Connect to VDD.

LDS1, LDS2

12, 46

CMOS-IN

Lock Detect Selection:

LDS1

LDS2

1

1

1

0

0

1

0

0

Lock mode

Auto 2000 ppm (default)

Auto 500 ppm

Manual select BB

Manual select PFC

VDD

3, 6, 9,11,15,21,26,

30, 33, 36, 40, 45

PWR

3.3 V power.

VDDA

47, 50

PWR

5 V power for VCO.

VEE

1, 13, 14, 27, 39

PWR

0 V power.

VEEA

51

PWR

0 V power for VCO.

NC

49

NC

No Connected.

Data Sheet Rev. 14

GD16367B/GD16368B

Page 8 of 14

相關PDF資料 |

PDF描述 |

|---|---|

| GD16522-48BA | CLOCK/DATA RECOVERY|BIPOLAR|QFP|48PIN|PLASTIC |

| GD16523-100BA | PCM, Other/Special/Miscellaneous |

| GD16524-100BA | CLOCK/DATA RECOVERY|QFP|100PIN|PLASTIC |

| GD16543-40AB | CLOCK/DATA RECOVERY|QFL|40PIN|CERAMIC |

| GD16543-40AC | CLOCK/DATA RECOVERY|LLCC|40PIN|CERAMIC |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| GD16368B-52BA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ATM/SONET Demultiplexer |

| GD16511 | 制造商:GIGA 功能描述: |

| GD16521 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2.5 GBIT/S RE TIMING LASER DRIVER |

| GD16521-48BA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2.5 GBIT/S RE TIMING LASER DRIVER |

| GD16521-D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2.5 GBIT/S RE TIMING LASER DRIVER |

發(fā)布緊急采購,3分鐘左右您將得到回復。