- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370311 > GD16367B-52BA ATM Multiplexer PDF資料下載

參數(shù)資料

| 型號: | GD16367B-52BA |

| 英文描述: | ATM Multiplexer |

| 中文描述: | ATM多路復(fù)用器 |

| 文件頁數(shù): | 2/14頁 |

| 文件大?。?/td> | 122K |

| 代理商: | GD16367B-52BA |

Functional Details, Both Devices

General

The GD16367B/GD16368B chip set pro-

vides transmission of 140 Mbit/s (E4) and

155 Mbit/s (STM-1/OC-3).

Both Optical NRZ signal transmission

and Electrical CMI-coded signal trans-

mission are supported by the internal

selectable CMI-Encoding/Decoding

circuitry.

Selectable 2/4/8 bit system interface is

provided.

140/155 Mbit/s and NRZ/CMI

Clock Frequencies

The VCO tuning range covers the clock

frequencies of 280 MHz to 311 MHz. The

actual clock frequency is determined by

reference clocks and received data.

The 280/311 MHz are used for CMI-oper-

ation. When operating in NRZ-mode the

VCO clock is divided by 2.

NRZ/CMI and Parallel Width

Selection

The devices can operate in different line

and system modes; selected by SEL1,

PW2, and PW1 (See Table 1).

The bit order at the system site is defined

with bit 0 as the first bit transferred (DIN0

for the transmitter and DOU0 for the re-

ceiver).

Line/System Loop Back

Connecting the differential Line Loop sig-

nals and clocks (LLxxx) from GD16368B

to GD16367B allows loop-back of the re-

ceived and recovered line signal, when

LLB is high on both devices. The Line

Loop back is also called remote loop

back.

Connecting the differential System Loop

signals (SLxxx) from GD16367B to

GD16368B allows system loop back,

when SLB is high on both devices. The

System Loop back is also called a local

loop back.

Loop Filters

Both circuits comprise fully integrated

PLL functions for re-timing data at the

transmit site, and for clock and data re-

covery at the receive site.

A passive loop filter consisting of a resis-

tor and a capacitor is used for each de-

vice. The external loop filters are

terminated to VEEA as shown in

Figure 1

(for the transmitter) and

Figure 4

(for the

receiver).

The loop filter values are optimised at the

evaluation board GD90367/368. The op-

timal values depend on the actual appli-

cation. The suggested values in

Figures

1

and

4

can be used as starting point for

the optimisation.

Data Sheet Rev. 14

GD16367B/GD16368B

Page 2 of 14

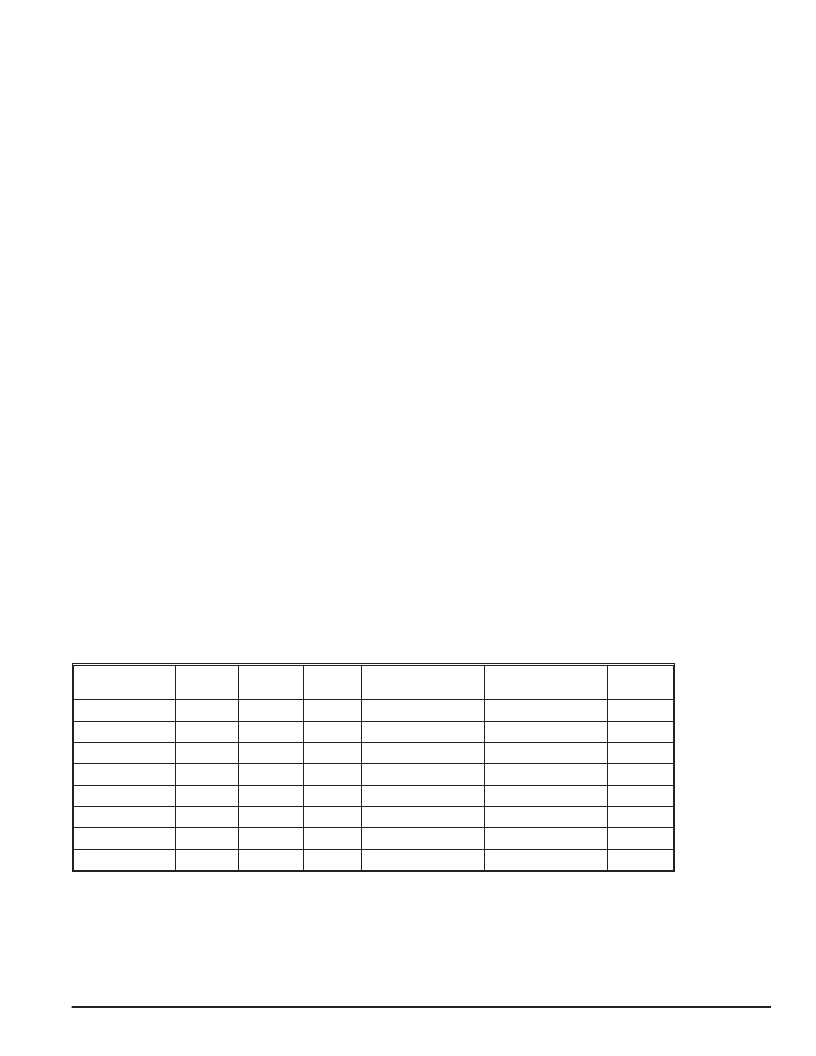

Mode

SEL1

PW2

PW1

Line Clock

[

Frequency/MHz]

System Clock

[Frequency/MHz]

Used Bits

CMI, 2 bit

0

0

0

280/311

70/78

0 & 1

CMI, 4 bit

0

0

1

280/311

35/39

0...3

CMI, 8 bit

0

1

0

280/311

17/19

0...8

Not valid

0

1

1

-

-

-

NRZ, 2 bit

1

0

0

140/155

70/78

0 & 1

NRZ, 4 bit

1

0

1

140/155

35/39

0...3

NRZ, 8 bit

1

1

0

140/155

17/19

0...8

Not valid

1

1

1

-

-

-

Table 1

NRZ/CMI and parallel width selection. This table is common for both devices.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GD16522-48BA | CLOCK/DATA RECOVERY|BIPOLAR|QFP|48PIN|PLASTIC |

| GD16523-100BA | PCM, Other/Special/Miscellaneous |

| GD16524-100BA | CLOCK/DATA RECOVERY|QFP|100PIN|PLASTIC |

| GD16543-40AB | CLOCK/DATA RECOVERY|QFL|40PIN|CERAMIC |

| GD16543-40AC | CLOCK/DATA RECOVERY|LLCC|40PIN|CERAMIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GD16368B-52BA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ATM/SONET Demultiplexer |

| GD16511 | 制造商:GIGA 功能描述: |

| GD16521 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2.5 GBIT/S RE TIMING LASER DRIVER |

| GD16521-48BA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2.5 GBIT/S RE TIMING LASER DRIVER |

| GD16521-D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2.5 GBIT/S RE TIMING LASER DRIVER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。