- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379098 > CYD36S18V18 (Cypress Semiconductor Corp.) FullFlex Synchronous SDR Dual-Port SRAM(FullFlex同步SDR雙端口SRAM) PDF資料下載

參數(shù)資料

| 型號: | CYD36S18V18 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | FullFlex Synchronous SDR Dual-Port SRAM(FullFlex同步SDR雙端口SRAM) |

| 中文描述: | FullFlex器件特別提款權(quán)同步雙端口SRAM(FullFlex器件同步雙端口SRAM的特別提款權(quán)) |

| 文件頁數(shù): | 51/52頁 |

| 文件大小: | 774K |

| 代理商: | CYD36S18V18 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁當(dāng)前第51頁第52頁

FullFlex

Document #: 38-06082 Rev. *F

Page 51 of 52

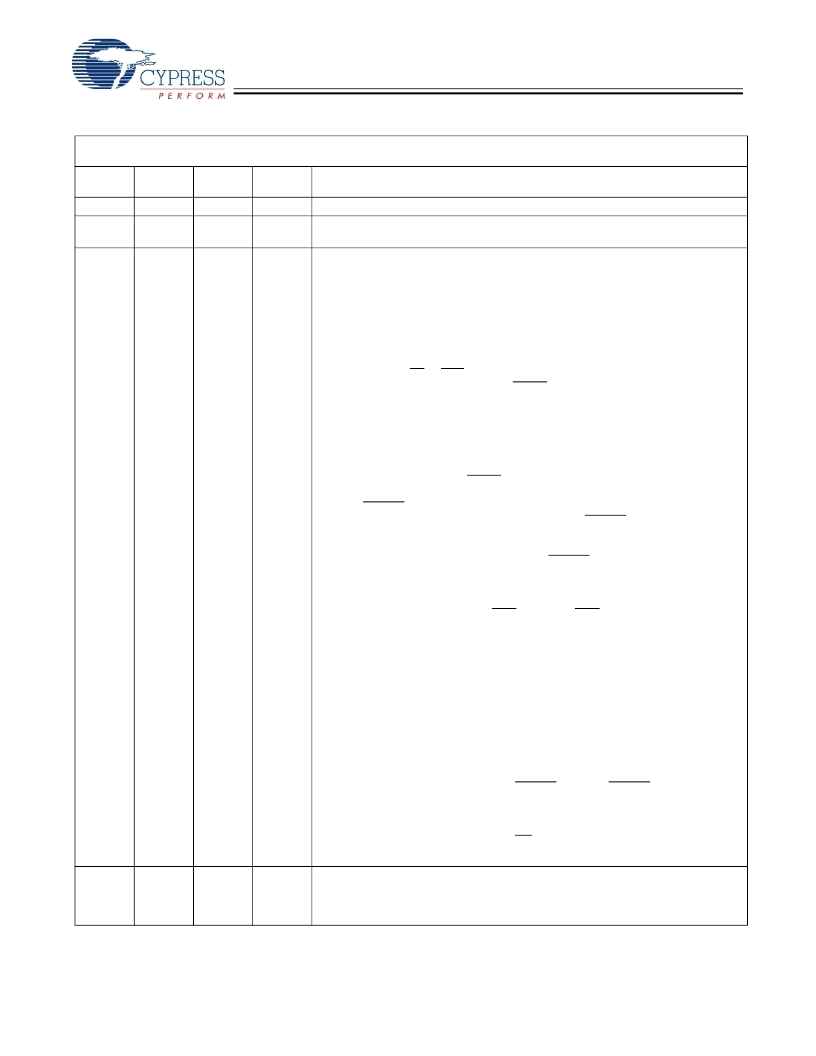

Document History Page

Document Title: FullFlex Synchronous SDR Dual-Port SRAM

Document Number: 38-06082

Issue

Date

Change

**

302411

See ECN

*A

334036

See ECN

REV.

ECN NO.

Orig. of

Description of Change

YDT

YDT

New data sheet

Corrected typo on page 1

Reproduced PDF file to fix formatting errors

Added statement about no echo clocks for flow-through mode

Updated electrical characteristics

Added note 16 and 17 (1.5V timing)

Added note 33 (timing for x18 devices)

Updated input edge rate (note 34)

Updated table 5 on deterministic access control logic

Added description of busy readback in deterministic access control section

Changed dummy write descriptions

Updated ZQ pins connection details

Updated note 24, B0 to BE0

Added power supply requirements to MRST and VC_SEL

Added note 4 (VIM disable)

Updated supply voltage to ground potential to 4.1V

Updated parameters on table 15

Updated and added parameters to table 16

Updated x72 pinout to SDR only pinout

Updated 484 PBGA pin diagram

Updated the pin definition of MRST

Updated the pin definition of VC_SEL

Updated READY description to include Wired OR note

Updated master reset to include wired OR note for READY

Updated minimum V

OH

value for the 1.8V LVCMOS configuration

Updated electrical characteristics to include I

OH

and I

OL

values

Updated electrical characteristics to include READY

Added I

IX3

Updated maximum input capacitance

Added Notes 33 and 34Removed Notes 15 and 17

Updated Pin Definitions for CQ0, CQ0

,

CQ1

,

and CQ1

Removed -100 Speed bin from Table.1 Selection Guide

Changed voltage name from V

DDQ

to V

DDIO

Changed voltage name from V

DD

to V

CORE

Moved the Mailbox Interrupt Timing Diagram to be the final timing diagram

Updated the Package Type for the CYD36S18V18 parts

Updated the Package Type for the CYD36S18V18 parts

Updated the Package Type for the CYD18S18V18 parts

Updated the Package Type for the CYD18S36V18 parts

Included the Package Diagram for the 256-Ball FBGA (19 x 19 mm) BW256

Included an OE Controlled Write for Flow-through Mode Switching Waveform

Included a Read with Echo Clock Switching Waveform

Updated Figure 5 and Figure 6

Updated Electrical Characteristics for READY V

OH

and READY V

Updated Electrical Characteristics for V

OH

and V

OL

for the -167 and -133 speeds

Included a Unit column for Table 5

Removed Switching Characteristic t

CA

from chart

Included t

OHZ

in Switching Waveform OE Controlled Write for Pipelined Mode

Included t

CKLZ2

in Waveform Read-to-Write-to-Read for Flow-through Mode

Updated AC Test Load and Waveforms

Included FullFlex36 SDR 484-ball BGA Pinout (Top View)

Included FullFlex18 SDR 484-ball BGA Pinout (Top View)

Included Timing Parameter t

CORDY

*B

395800

See ECN

SPN

*C

402238

SEE ECN

KGH

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CYD36S36V18 | FullFlex Synchronous SDR Dual-Port SRAM(FullFlex同步SDR雙端口SRAM) |

| CYD18S72V | FLEx72 3.3V 64K/128K/256K x 72 Synchronous Dual-Port RAM(FLEx72 3.3V 64K/128K/256K x 72同步雙端口RAM) |

| CYD09S72V | FLEx72 3.3V 64K/128K/256K x 72 Synchronous Dual-Port RAM(FLEx72 3.3V 64K/128K/256K x 72同步雙端口RAM) |

| CYDC128B08-55AXC | 1.8V 4k/8k/16k x 16 and 8k/16k x 8 ConsuMoBL Dual-Port Static RAM |

| CYDC064B08 | 1.8V 4k/8k/16k x 16 and 8k/16k x 8 ConsuMoBL Dual-Port Static RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CYD36S18V18-133BBXC | 制造商:Cypress Semiconductor 功能描述:FULLFLEX36 36M SYNC DUAL-PORT ?2M X 18, SDR? - Bulk |

| CYD36S18V18-167BGXC | 功能描述:靜態(tài)隨機(jī)存取存儲器 18MB (2Mx18) 1.8v 167MHz Sync 靜態(tài)隨機(jī)存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CYD36S18V18-167BGXI | 功能描述:靜態(tài)隨機(jī)存取存儲器 36MB (2Mx18) 1.8v 167MHz Sync 靜態(tài)隨機(jī)存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CYD36S18V18-200BGXC | 功能描述:靜態(tài)隨機(jī)存取存儲器 36MB (2Mx18) 1.8v 200MHz Sync 靜態(tài)隨機(jī)存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CYD36S36V18-133BBXC | 功能描述:IC SRAM 36MBIT 133MHZ 256LFBGA RoHS:是 類別:集成電路 (IC) >> 存儲器 系列:- 標(biāo)準(zhǔn)包裝:1,000 系列:- 格式 - 存儲器:RAM 存儲器類型:移動 SDRAM 存儲容量:256M(8Mx32) 速度:133MHz 接口:并聯(lián) 電源電壓:1.7 V ~ 1.95 V 工作溫度:-40°C ~ 85°C 封裝/外殼:90-VFBGA 供應(yīng)商設(shè)備封裝:90-VFBGA(8x13) 包裝:帶卷 (TR) 其它名稱:557-1327-2 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。