- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379075 > CY7C1464AV25 (Cypress Semiconductor Corp.) 36-Mbit (1M x 36/2M x 18/512K x 72) Pipelined SRAM with NoBL Architecture(帶NoBL結(jié)構(gòu)的36-Mbit (1M x 36/2M x 18/512K x 72) Pipelined SRAM) PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C1464AV25 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | 36-Mbit (1M x 36/2M x 18/512K x 72) Pipelined SRAM with NoBL Architecture(帶NoBL結(jié)構(gòu)的36-Mbit (1M x 36/2M x 18/512K x 72) Pipelined SRAM) |

| 中文描述: | 36兆位(1米x 36/2M x 18/512K × 72)流水線的SRAM架構(gòu)的總線延遲(帶總線延遲結(jié)構(gòu)的36兆位(1米x 36/2M x 18/512K × 72)流水線的SRAM) |

| 文件頁數(shù): | 16/27頁 |

| 文件大小: | 465K |

| 代理商: | CY7C1464AV25 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁

CY7C1460AV25

CY7C1462AV25

CY7C1464AV25

Document #: 38-05354 Rev. *D

Page 16 of 27

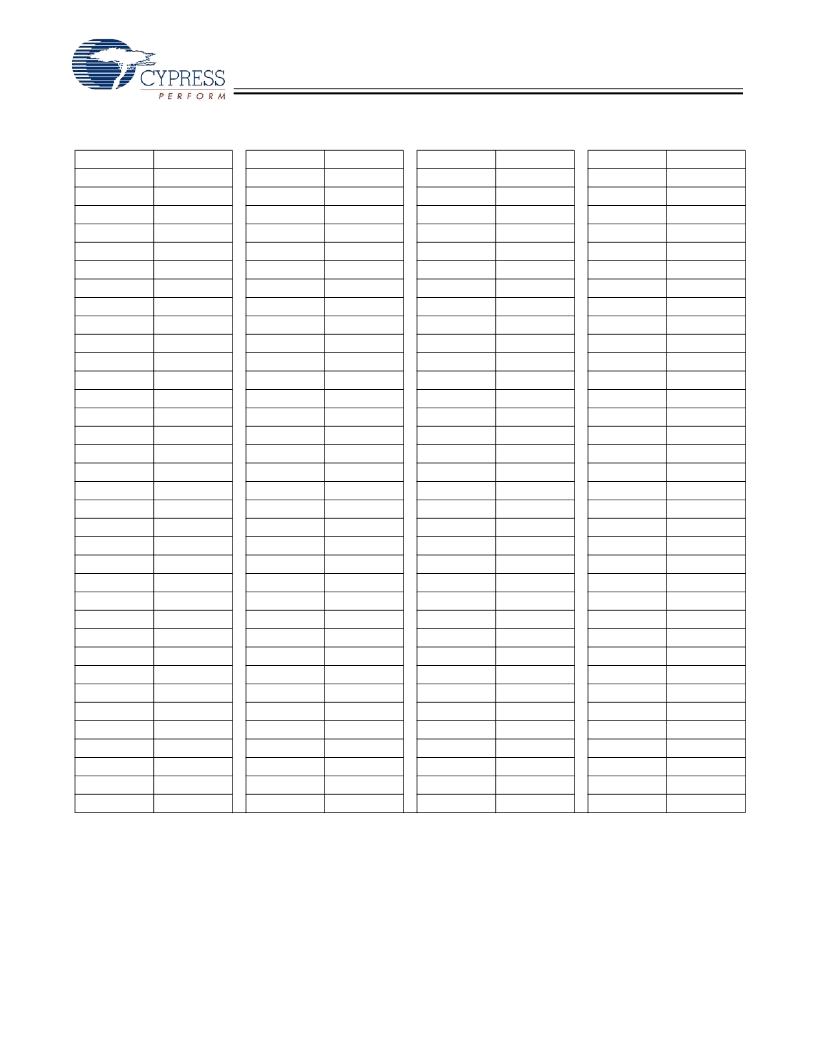

209-ball FBGA Boundary Scan Order

[12, 13]

CY7C1464AV25 (512K x 72)

Bit#

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

Ball ID

W6

V6

U6

W7

V7

U7

T7

V8

U8

T8

V9

U9

P6

W11

W10

V11

V10

U11

U10

T11

T10

R11

R10

P11

P10

N11

N10

M11

M10

L11

L10

K11

M6

L6

J6

Bit#

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

Ball ID

F6

K8

K9

K10

J11

J10

H11

H10

G11

G10

F11

F10

E10

E11

D11

D10

C11

C10

B11

B10

A11

A10

C9

B9

A9

D8

C8

B8

A8

D7

C7

B7

A7

D6

G6

Bit#

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

Ball ID

H6

C6

B6

A6

A5

B5

C5

D5

D4

C4

A4

B4

C3

B3

A3

A2

A1

B2

B1

C2

C1

D2

D1

E1

E2

F2

F1

G1

G2

H2

H1

J2

J1

K1

N6

Bit#

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

Ball ID

K3

K4

K6

K2

L2

L1

M2

M1

N2

N1

P2

P1

R2

R1

T2

T1

U2

U1

V2

V1

W2

W1

T6

U3

V3

T4

T5

U4

V4

W5

V5

U5

Internal

Note:

13.Bit# 138 is preset HIGH.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C1462AV25 | 36-Mbit (1M x 36/2M x 18/512K x 72) Pipelined SRAM with NoBL Architecture(帶NoBL結(jié)構(gòu)的36-Mbit (1M x 36/2M x 18/512K x 72) Pipelined SRAM) |

| CY7C1460AV33 | 36-Mbit (1M x 36/2M x 18/512K x 72) Pipelined SRAM with NoBL Architecture(帶NoBL結(jié)構(gòu)的36-Mbit (1M x 36/2M x 18/512K x 72) Pipelined SRAM) |

| CY7C1464AV33 | 36-Mbit (1M x 36/2M x 18/512K x 72) Pipelined SRAM with NoBL Architecture(帶NoBL結(jié)構(gòu)的36-Mbit (1M x 36/2M x 18/512K x 72) Pipelined SRAM) |

| CY7C1462AV33 | 36-Mbit (1M x 36/2M x 18/512K x 72) Pipelined SRAM with NoBL Architecture(帶NoBL結(jié)構(gòu)的36-Mbit (1M x 36/2M x 18/512K x 72) Pipelined SRAM) |

| CY7C1472V33-167AXI | 72-Mbit (2M x 36/4M x 18/1M x 72) Pipelined SRAM with NoBL Architecture |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1464AV25-167BGC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 512kx72 36M NoBL PL 靜態(tài)隨機(jī)存取存儲(chǔ)器 COM RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1464AV25-167BGCES | 制造商:Cypress Semiconductor 功能描述:36MB NOBL 512KB X 72 PIPELINE 2.5V - Bulk |

| CY7C1464AV25-200BGC | 制造商:Cypress Semiconductor 功能描述:SRAM SYNC OCTAL 2.5V 36MBIT 512KX72 3.2NS 209FBGA - Bulk |

| CY7C1464AV33-167BGI | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 512Kx72 3.3V NoBL PL 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C146-55JC | 制造商:Cypress Semiconductor 功能描述:SRAM Chip Async Dual 5V 16K-Bit 2K x 8 55ns 52-Pin PLCC 制造商:Cypress Semiconductor 功能描述:2K X 8 DUAL-PORT SRAM, 55 ns, PQCC52 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。