- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366628 > C9827JY Up to 5A ULDO linear regulator PDF資料下載

參數(shù)資料

| 型號: | C9827JY |

| 英文描述: | Up to 5A ULDO linear regulator |

| 中文描述: | CPU系統(tǒng)時(shí)鐘發(fā)生器| SSOP封裝| 56PIN |塑料 |

| 文件頁數(shù): | 4/25頁 |

| 文件大小: | 170K |

| 代理商: | C9827JY |

C9827J

High Performance Pentium 4 Clock Synthesizer

Cypress Semiconductor Corporation

525 Los Coches St.

Milpitas, CA 95035. Tel: 408-263-6300, Fax: 408-263-6571

http://www.cypress.com

Document#: 38-07107 Rev. **

5/24/2001

Page 4 of 25

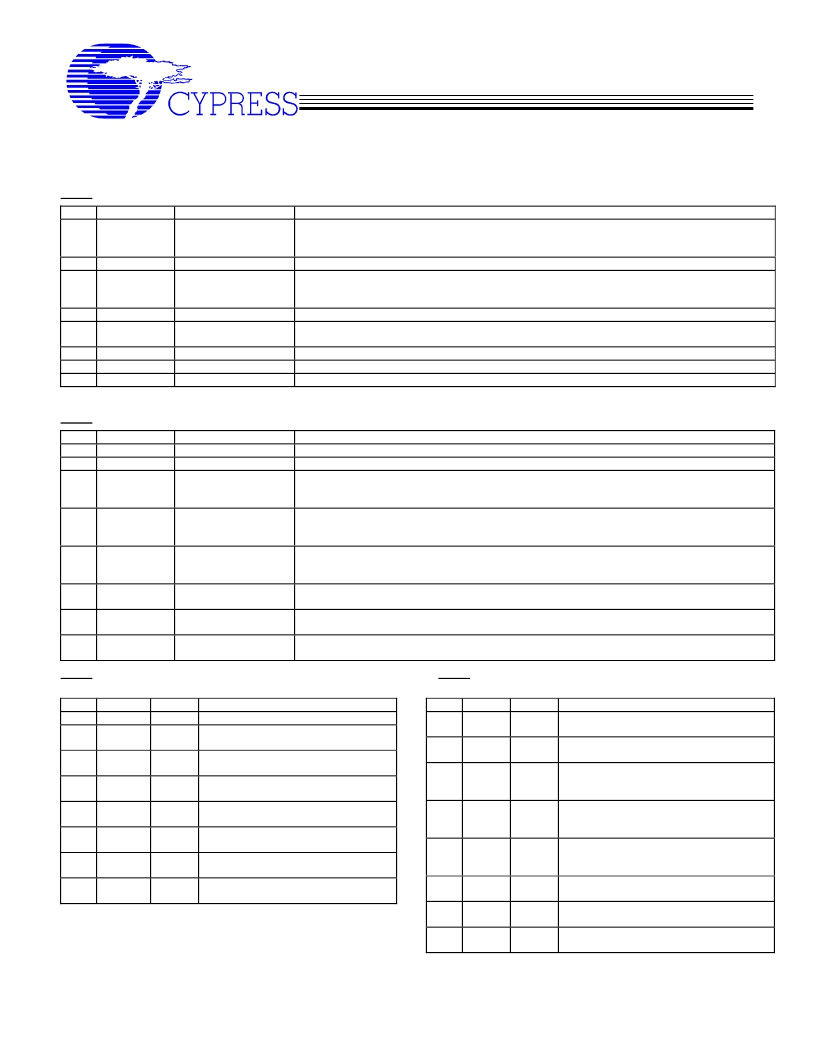

Serial Control Registers (Cont.)

Byte 0: CPU Clock Register

Bit

7

@Pup

0

Pin#

-

Description

Spread Spectrum Enable

0 = Spread Off, 1 = Spread On

This is a Read and Write control bit.

S1/S3 Mode Select. 0=S1(default) 1=S3 (see

note A)

3V66_1/VCH frequency Select

0 = 66M selected, 1 = 48M selected

This is a Read and Write control bit.

CPU_STP#. Reflects the current value of the external CPU_STP# (pin 53) This bit is Read Only.

Reflects the current value of the internal PCI_STP# function when read. Internally PCI_STP# is a

logical AND function of the internal SMBus register bit and the external PCI_STP# pin.

Frequency Select Bit 2. Reflects the value of SEL2 (pin 40). This bit is Read Only.

Frequency Select Bit 1. Reflects the value of SEL1 (pin 55). This bit is Read Only.

Frequency Select Bit 0. Reflects the value of SEL0 (pin 54). This bit is Read Only.

6

5

0

0

-

35

4

3

Pin 53

Pin 34

44,45,48,49,51,52

10,11,12,13,16,17,18

2

1

0

Pin 40

Pin 55

Pin 54

-

-

-

Note A:

When this bit is asserted high “1”, All CPU clocks (TRUE & COMPLEMENT) will be disabled in Hi-Z,

to be pulled low externally through the

pull down resistors, R

LA

or R

LB

in fig. 1. This is only applicable when PD# is low. It is not applicable to CPU_STP#

Byte 1: CPU Clock Register

Bit

7

6

5

@Pup

Pin 43

0

0

Pin#

-

-

44,45

Description

MULT0 (Pin 43) Value. This bit is Read Only.

Reserved

Controls CPU2 functionality when CPU_STP# is asserted LOW

1 = Free Running, 0 = Stopped LOW with CPU_STP# asserted LOW

This is a Read and Write control bit.

Controls CPU1 functionality when CPU_STP# is asserted LOW

1 = Free Running, 0 = Stopped LOW with CPU_STP# asserted LOW

This is a Read and Write control bit.

Controls CPU0 functionality when CPU_STP# is asserted LOW

1 = Free Running, 0 = Stopped LOW with CPU_STP# asserted LOW

This is a Read and Write control bit.

CPU2 Output Control, 1 = enabled, 0 = disable HIGH and CPU/2 disables LOW

This is a Read and Write control bit.

CPU1 Output Control, 1 = enabled, 0 = disable HIGH and CPU/1 disables LOW

This is a Read and Write control bit.

CPU0 Output Control, 1 = enabled, 0 = disable HIGH and CPU/0 disables LOW

This is a Read and Write control bit.

4

0

48,49

3

0

51,52

2

1

44,45

1

1

48,49

0

1

51,52

Byte 2: PCI Clock Control Register

(all bits are read and write functional)

Bit

7

6

@Pup

0

1

Pin#

-

18

Description

Reserved

PCI6 Output Control

1 = enabled, 0 = forced LOW

PCI5 Output Control

1 = enabled, 0 = forced LOW

PCI4 Output Control

1 = enabled, 0 = forced LOW

PCI3 Output Control

1 = enabled, 0 = forced LOW

PCI2 Output Control

1 = enabled, 0 = forced LOW

PCI1 Output Control

1 = enabled, 0 = forced LOW

PCI0 Output Control

1 = enabled, 0 = forced LOW

5

1

17

4

1

16

3

1

13

2

1

12

1

1

11

0

1

10

Byte 3: PCI_F Clock and 48M Control Register

(all bits are read and write functional)

Bit

7

@Pup

1

Pin#

38

Description

48MDOT Output Control

1 = enabled, 0 = forced LOW

48MUSB Output Control

1 = enabled, 0 = forced LOW

PCI_STP#, control of PCI_F2.

0 = Free Running, 1 = Stopped when

PCI_STP# is LOW

PCI_STP#, control of PCI_F1.

0 = Free Running, 1 = Stopped when

PCI_STP# is LOW

PCI_STP#, control of PCI_F0.

0 = Free Running, 1 = Stopped when

PCI_STP# is LOW

PCI_F2 Output Control

1=running, 0=forced LOW

PCI_F1 Output Control

1= running, 0=forced LOW

PCI_F0 Output Control

1= running, 0=forced LOW

6

1

39

5

0

7

4

0

6

3

0

5

2

1

7

1

1

6

0

1

5

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| C9832HT | Up to 5A ULDO linear regulator |

| C9832HY | N-CHANNEL 60V - 0.014 Ohm - 60A TO-220/TO220FP STRIPFET POWER MOSFET |

| C9860-21 | 3 BAND EQUALIZER AUDIO PROCESSOR WITH SUBWOOFER CONTROL |

| C9860-22 | QUAD 2 CHANNEL MULTIPLEXER |

| C9860-23 | QUAD 2 CHANNEL MULTIPLEXER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| C982P | 制造商:PERKINELMER 制造商全稱:PerkinElmer Optoelectronics 功能描述:CHANNEL PHOTO MULTIPLIER |

| C983 | 制造商:PERKINELMER 制造商全稱:PerkinElmer Optoelectronics 功能描述:CHANNEL PHOTO MULTIPLIER |

| C9832HT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CPU SYSTEM CLOCK GENERATOR|TSSOP|56PIN|PLASTIC |

| C9832HY | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CPU SYSTEM CLOCK GENERATOR|SSOP|56PIN|PLASTIC |

| C98332-000 | 制造商:TE Connectivity 功能描述:QLL405 - Labels that come on sheets or rolls 制造商:TE Connectivity 功能描述:C98332-000 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。