- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1906 > BBT3420-SN (Intersil)TXRX QUAD MULTI-RATE 289-EBGA PDF資料下載

參數(shù)資料

| 型號: | BBT3420-SN |

| 廠商: | Intersil |

| 文件頁數(shù): | 11/38頁 |

| 文件大小: | 0K |

| 描述: | TXRX QUAD MULTI-RATE 289-EBGA |

| 標準包裝: | 84 |

| 類型: | 收發(fā)器 |

| 驅(qū)動器/接收器數(shù): | 4/4 |

| 規(guī)程: | XAUI,XGMII,MDC/MDIO |

| 電源電壓: | 1.7 V ~ 1.9 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 289-BGA |

| 供應商設(shè)備封裝: | 289-BGA(19x19) |

| 包裝: | 托盤 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁

19

9

TX_SDR

1 = SDR

0 = DDR

0’b

R/W

Single data rate on XGMII interface of transmitter.

8VDDQ_ASNS_EN 0=enable

1=disable

0’b

R/W

Automatically detect VDDQ power supply level and adjust

parallel output buffer driving strength.

7

HSTL_DRIVE

0=enable

1=disable

0’b

R/W

Increase parallel output buffer driving strength (if autosense

disabled).

6:4

LOS_CONTROL

0’h = 160mVP-P

1’h = 240mVP-P

2’h = 200mVP-P

3’h = 120mVP-P

4’h = 80mVP-P

else = 160mVP-P

000’b

R/W

Set the threshold voltage for the Loss Of Signal (LOS)

detection circuit. Nominal levels are listed for each control

value. Note 2

3

SC_RBC

1=source sync

0=source center

0’b

R/W

Timing of outgoing Receive Byte Clock (RBC) to Receive data

2

AKR_EN

1 = enable random

A/K/R

0 = /K/ only

0’b

R/W

Enable pseudo-random A/K/R (Note 1) in Inter Packet Gap

(IPG) on transmitter side (vs. /K/ only)

1

SOFT_RESET

Write 1 to initiate.

0’b

R/W SC

Reset the entire chip except MII register settings

0

Reserved

NOTES:

1. These state machines are implemented according to 802.3ae-2002 clause 48.

2. Please refer to section “3.7.2 Loss of Signal (LOS)” on page 6 for a more detailed description.

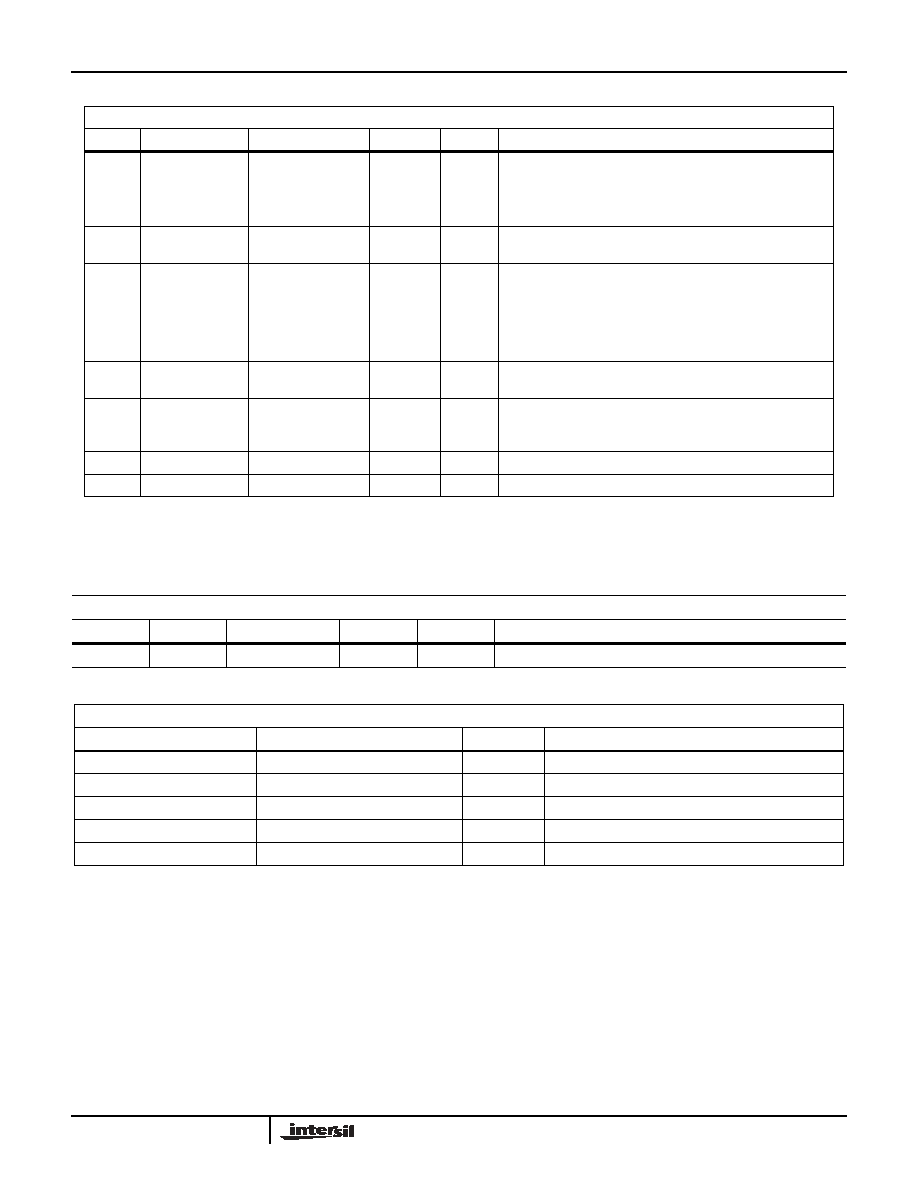

TABLE 3-28. MISCELLANEOUS CONTROL REGISTER 3 (CLAUSE 22) (Continued)

MII REgister 29, ADDRESS = 1D’h

BIT

NAME

SETTING

DEFAULT

R/W

DESCRIPTION

TABLE 3-29. SPECIAL TEST FUNCTION CONTROL REGISTER

MII REGISTER 30 & 49159, ADDRESSES = 1E’h & C007’h

BIT

NAME

SETTING

DEFAULT

R/W

DESCRIPTION

15:0

reserved

AAAA’h

R/W

Internal Function. DO NOT ALTER THIS REGISTER in BBT3420

TABLE 3-30. HALF RATE CLOCK CONTROL REGISTER

MII REGISTER 31 & 49160, ADDRESSES = 1F’h & C008’h

BIT

NAME

SETTING

DEFAULT

R/W

DESCRIPTION

15:4

reserved

0’h

R/W

3

HALF_RATED

1’b = half rate clock

0’b

R/W

Channel D is running at half-rate clock speed

2

HALF_RATEC

1’b = half rate clock

0’b

R/W

Channel C is running at half-rate clock speed

1

HALF_RATEB

1’b = half rate clock

0’b

R/W

Channel B is running at half-rate clock speed

0

HALF_RATEA

1’b = half rate clock

0’b

R/W

Channel A is running at half-rate clock speed

BBT3420

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BD3843FS-E2 | IC SOUND PROCESSOR 6CH 24SSOP |

| BD9251FV-E2 | IC PREAMP HBD PIR SENSOR 14-SSOP |

| BGF 104C E6327 | IC HSMMC FILTER/ESD PROT S-WLP-6 |

| BGF 104C E6328 | IC HSMMC FILTER/ESD PROT WLP-16 |

| BGF 110 E6327 | IC MEMORY CARD PROTECT S-WLP-24 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BBT3421 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:4 Channel Multi-rate Intelligent CMOS Re-Timer |

| BBT3821 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Octal 2.488Gbps to 3.187Gbps/ Lane Retimer |

| BBT3821-JH | 功能描述:IC RE-TIMER OCTAL 192-BGA RoHS:否 類別:集成電路 (IC) >> 時鐘/計時 - 專用 系列:- 標準包裝:1,500 系列:- 類型:時鐘緩沖器/驅(qū)動器 PLL:是 主要目的:- 輸入:- 輸出:- 電路數(shù):- 比率 - 輸入:輸出:- 差分 - 輸入:輸出:- 頻率 - 最大:- 電源電壓:3.3V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-SSOP(0.209",5.30mm 寬) 供應商設(shè)備封裝:28-SSOP 包裝:帶卷 (TR) 其它名稱:93786AFT |

| BBT3821LP-JH | 功能描述:IC RE-TIMER OCTAL 192-BGA RoHS:否 類別:集成電路 (IC) >> 時鐘/計時 - 專用 系列:- 標準包裝:1,500 系列:- 類型:時鐘緩沖器/驅(qū)動器 PLL:是 主要目的:- 輸入:- 輸出:- 電路數(shù):- 比率 - 輸入:輸出:- 差分 - 輸入:輸出:- 頻率 - 最大:- 電源電壓:3.3V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-SSOP(0.209",5.30mm 寬) 供應商設(shè)備封裝:28-SSOP 包裝:帶卷 (TR) 其它名稱:93786AFT |

| BBTEKIT | 功能描述:剝線和切削工具 COMPR AND STRIP TOOL KIT FOR RG59 RG6 CBL RoHS:否 制造商:Molex 產(chǎn)品:Cable Strippers 類型: 描述/功能:Stripper |

發(fā)布緊急采購,3分鐘左右您將得到回復。