- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366550 > AM79C90PCTR (Advanced Micro Devices, Inc.) CMOS Local Area Network Controller for Ethernet (C-LANCE) PDF資料下載

參數(shù)資料

| 型號: | AM79C90PCTR |

| 廠商: | Advanced Micro Devices, Inc. |

| 英文描述: | CMOS Local Area Network Controller for Ethernet (C-LANCE) |

| 中文描述: | 的CMOS局域網(wǎng)控制器(丙應(yīng)聘以太網(wǎng)) |

| 文件頁數(shù): | 56/62頁 |

| 文件大?。?/td> | 437K |

| 代理商: | AM79C90PCTR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁當(dāng)前第56頁第57頁第58頁第59頁第60頁第61頁第62頁

56

Am79C90

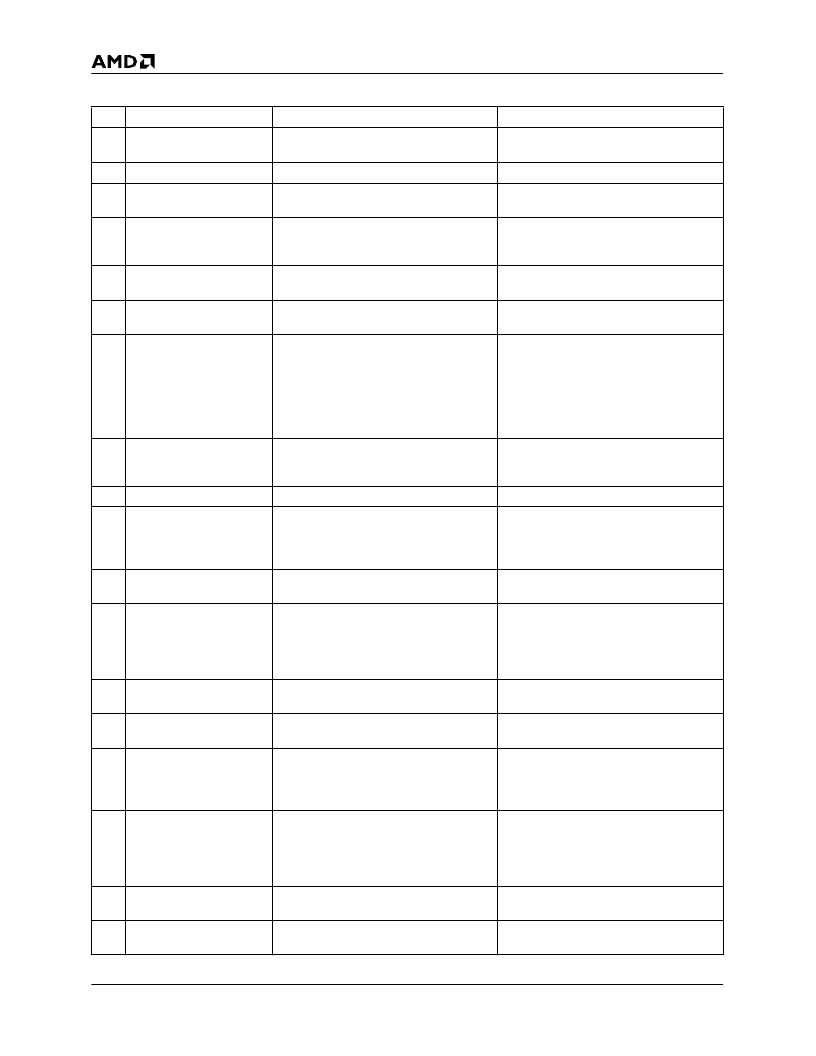

Table B-1. Comparison Summary of the C-LANCE and LANCE Devices

Description

Am79C90 C-LANCE

Am7990 LANCE

1

Process/Power

Consumption

0.8-micron CS-21S CMOS process

I

CC

≤

50 mA

Dual FIFOs: 48-byte TX, 64-byte RX

NS-8B NMOS process

I

CC

≤

270 mA

Single FIFO: 48-byte TX/RX

2

FIFOs

3

Transmit Lockout Due to

Receive

Will not occur with dual FIFOs and

enhanced microcode.

May occur in high receive rate situations

with “l(fā)ess than optimal” bus latencies.

4

Per-Packet FCS

Transmit descriptor bit is used to allow per-

packet addition of CRC when DTCR is set in

the MODE register.

No per-packet CRC control provided.

5

Backoff Algorithm

Selectable Modified Backoff Algorithm or

standard backoff algorithm.

Only standard backoff algorithm available.

6

TX Descriptor Zero Buffer

Byte Count Capability

Allows TX buffer byte count of zero.

No capability for TX buffer byte count of zero.

7

Interframe Spacing (IFS)

Behavior

a) Implements two-part deferral after

transmit

b) Part 1 of two-part deferral after receive is

6

μ

s

c) Heartbeat window = 4

d) Receive blind time after receive less than

500 ns

μ

s

a) One-part deferral after transmit

b) Part 1 of two-part deferral after receive is

4.1

μ

s

c) Heartbeat window = 2

d) Receive blind time after receive = 4.1

μ

s

μ

s

8

“Heartbeat OK” (No CERR)

Definition

Heartbeat OK if collision is asserted at any

time from the beginning of the transmission

to the end of the heartbeat window.

Heartbeat OK if collision is asserted during

the heartbeat window.

9

Receive Lockup

Will not occur.

May occur when bus latency is large.

10

ALE Behavior

ALE may be driven HIGH at end of bus

mastership when ACON is set to 0. When

ACON is set to 1, ALE is not driven LOW at

end of bus mastership period.

ALE may be driven LOW at end of bus

mastership when ACON is set to 1. When

ACON is set to 0, ALE is not driven HIGH at

end of bus mastership period.

11

External Loopback on a Live

Network

No problems.

May receive invalid loopback failure

indications.

12

Software Reset (STOP Bit)

Handling

a) STOP bit in CSR0 is latched. When STOP

is set, the slave cycle is allowed to

complete before the C-LANCE resets.

b) CSR1 and CSR2 contents are preserved

when the STOP bit is set to one.

a) STOP bit in CSR0 not latched and will

reset the device immediately when

written.

b) CSR1 and CSR2 are not preserved when

the STOP bit is set to one.

13

CSR0 Slave Read Data

Stability

CSR0 latched during Slave reads to

guarantee timing on DAL lines.

CSR0 not latched during Slave read cycles

(could give timing violations on DAL lines).

14

INEA Bit Behavior

INEA bit can be set in CSR0 at any time,

regardless of the state of the STOP bit.

INEA cannot be set in CSR0 while the STOP

bit is set.

15

Effect of Setting the STOP

Bit on CSR0 Bits

Setting the STOP bit in CSR0 when the

STOP bit is already set does not affect any

of the other bits in CSR0 (they are not

cleared).

Setting the STOP bit in CSR0 causes all of

the other bits in CSR0 to clear, regardless of

the previous state of the STOP bit.

16

AC Specification Changes

#06 (t

#08 (t

#18 (t

#30 (t

#45 (t

TEP

) maximum = 60 ns

) maximum = 60 ns

) minimum = 35 ns

) minimum = 40 ns

) minimum = 65 ns

TDP

RDS

RDAS

RDYS

#06 (t

#08 (t

#18 (t

#30 (t

#45 (t

TEP

) maximum = 70 ns

) maximum = 70 ns

) minimum = 40 ns

) minimum = 50 ns

) minimum = 75 ns

TDP

RDS

RDAS

RDYS

17

Burn-In Option

The burn-in option for the C-LANCE is no

longer available.

18

RX Descriptor Zero Buffer

Byte Count Handling

Unpredictable results when the RX

Descriptor Buffer Byte Count is set to zero.

Interprets a BCNT field setting of zero in a

receive descriptor as a 4096-byte buffer.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C930 | PCnet-Mobile Single-Chip Wireless LAN Media Access Controller |

| AM79C930VCW | PCnet-Mobile Single-Chip Wireless LAN Media Access Controller |

| AM79C940VCW | Media Access Controller for Ethernet (MACE) |

| AM79C940 | Media Access Controller for Ethernet (MACE) |

| AM79C940JCW | Media Access Controller for Ethernet (MACE) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C90WW WAF | 制造商:Advanced Micro Devices 功能描述: |

| AM79C930 | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet-Mobile Single-Chip Wireless LAN Media Access Controller |

| AM79C930EVAL-HW | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Am79C930EVAL-HW - PCnet-Mobile Evaluation Kit |

| AM79C930VC/W | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet-Mobile Single-Chip Wireless LAN Media Access Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。