- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1987 > AD9600ABCPZ-150 (Analog Devices Inc)IC ADC 10BIT 150MSPS 64LFCSP PDF資料下載

參數(shù)資料

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)當(dāng)前第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)

AD9600

Rev. B | Page 5 of 72

SPECIFICATIONS

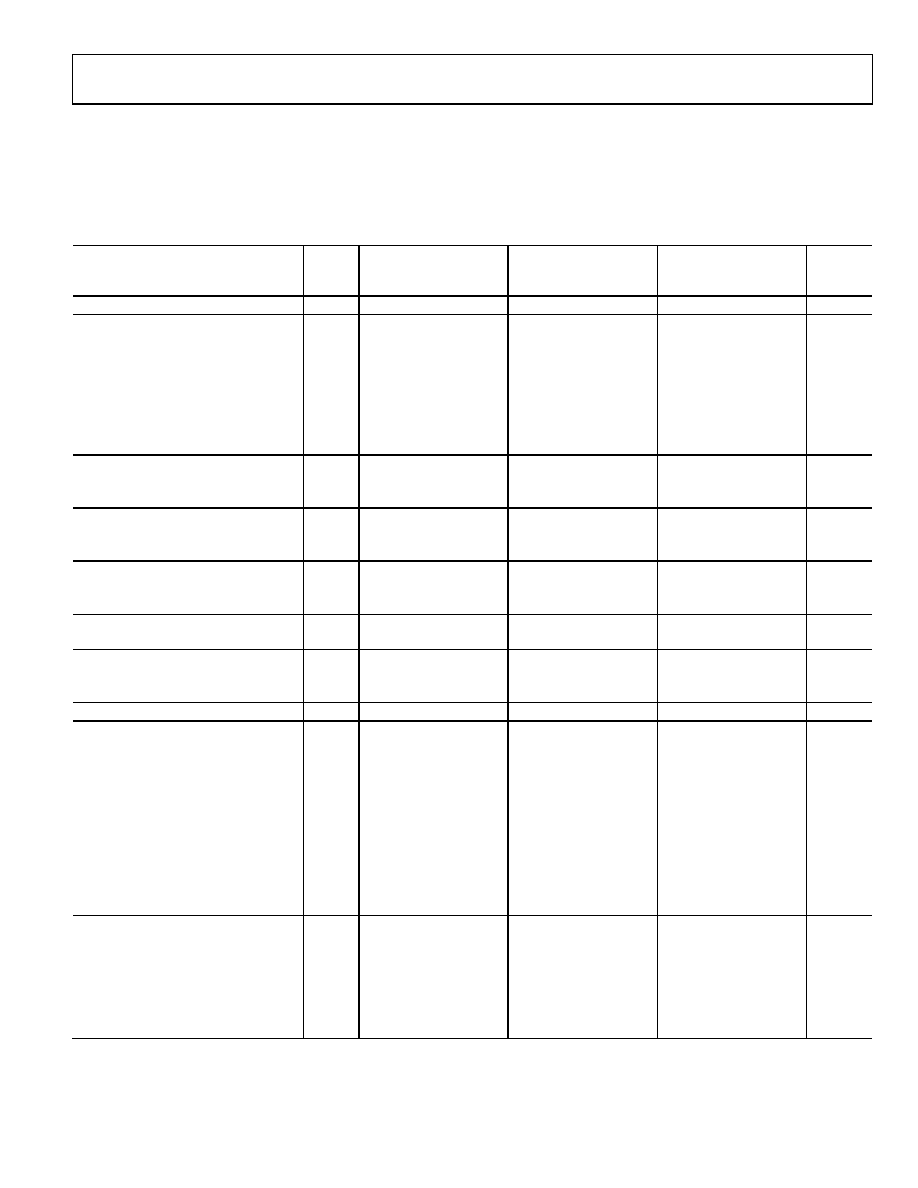

DC SPECIFICATIONS

AVDD = 1.8 V, DVDD = 1.8 V, DRVDD = 3.3 V, maximum sample rate, VIN = 1.0 dBFS differential input, 1.0 V internal reference,

DCS enabled, fast detect output pins disabled, signal monitor disabled, unless otherwise noted.

Table 1.

Parameter

Temp

AD9600ABCPZ-105/

AD9600BCPZ-105

AD9600ABCPZ-125/

AD9600BCPZ-125

AD9600ABCPZ-150/

AD9600BCPZ-150

Min

Typ

Max

Min

Typ

Max

Min

Typ

Max

Unit

RESOLUTION

Full

10

Bits

ACCURACY

No Missing Codes

Full

Guaranteed

Offset Error

Full

±0.3

±0.7

±0.3

±0.7

±0.3

±0.7

% FSR

Gain Error

Full

3.6

2.2

1.0

4.0

2.5

1.3

4.3

3.0

1.6

% FSR

Differential Nonlinearity (DNL)1

Full

±0.2

LSB

25°C

±0.1

LSB

Integral Nonlinearity (INL)1

Full

±0.3

±0.4

LSB

25°C

±0.1

LSB

MATCHING CHARACTERISTICS

Offset Error

Full

±0.3

±0.7

±0.3

±0.7

±0.2

±0.7

% FSR

Gain Error

Full

±0.2

±0.8

±0.3

±0.8

±0.2

±0.8

% FSR

TEMPERATURE DRIFT

Offset Error

Full

±15

ppm/°C

Gain Error

Full

±95

ppm/°C

INTERNAL VOLTAGE REFERENCE

Output Voltage Error (1 V Mode)

Full

±5

±16

±5

±16

±5

±16

mV

Load Regulation @ 1.0 mA

Full

7

mV

INPUT-REFERRED NOISE

VREF = 1.0 V

25°C

0.1

LSB rms

ANALOG INPUT

Input Span, VREF = 1.0 V

Full

2

V p-p

Input Capacitance2

Full

8

pF

VREF INPUT RESISTANCE

Full

6

kΩ

POWER SUPPLIES

Supply Voltage

AVDD, DVDD

Full

1.7

1.8

1.9

1.7

1.8

1.9

1.7

1.8

1.9

V

DRVDD (CMOS Mode)

Full

1.7

3.3

3.6

1.7

3.3

3.6

1.7

3.3

3.6

V

Supply Current

IAVDD1

Full

310

385

419

mA

IDVDD1

Full

34

42

50

mA

365

455

495

IDRVDD (3.3 V CMOS)

Full

35

36

42

mA

IDRVDD (1.8 V CMOS)

Full

15

18

22

mA

IDRVDD (1.8 V LVDS)

42

44

46

mA

POWER CONSUMPTION

DC Input

Full

600

650

750

800

825

890

mW

Sine Wave Input1

DRVDD = 1.8 V

Full

645

813

892

mW

DRVDD = 3.3 V

Full

740

900

990

mW

Standby Power3

Full

68

77

mW

Power-Down Power

Full

2.5

6

2.5

6

2.5

6

mW

1 Measured with a low input frequency, full-scale sine wave, with approximately 5 pF loading on each output bit.

2 Input capacitance refers to the effective capacitance between one differential input pin and AGND. Refer to Figure 8 for the equivalent analog input structure.

3 Standby power is measured with a dc input and the CLK+ and CLK pins inactive )set to AVDD or AGND.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9608BCPZRL7-125 | IC ADC 10BIT 125MSPS 64LFCSP |

| AD9609BCPZRL7-80 | IC ADC 10BIT SRL/SPI 80M 32LFCSP |

| AD9613BCPZ-170 | IC ADC 12BIT SRL 170MSPS 64LFCSP |

| AD9627ABCPZ-125 | IC ADC 12BIT 1255MSPS 64LFCSP |

| AD9627ABCPZ11-150 | IC ADC 11BIT 150MSPS 64LFCSP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9600BCPZ-105 | 制造商:Analog Devices 功能描述:ADC Dual Pipelined 105Msps 10-bit Parallel/LVDS 64-Pin LFCSP EP |

| AD9600BCPZ-125 | 制造商:Analog Devices 功能描述:ADC Dual Pipelined 125Msps 10-bit Parallel/LVDS 64-Pin LFCSP EP |

| AD9600BCPZ-150 | 制造商:Analog Devices 功能描述: |

| AD9601 | 制造商:AD 制造商全稱:Analog Devices 功能描述:10-Bit, 200 MSPS/250 MSPS 1.8 V Analog-to-Digital Converter |

| AD9601-250EBZ | 功能描述:數(shù)據(jù)轉(zhuǎn)換 IC 開發(fā)工具 10-Bit 250 Msps LowPwr CMOS ADC RoHS:否 制造商:Texas Instruments 產(chǎn)品:Demonstration Kits 類型:ADC 工具用于評(píng)估:ADS130E08 接口類型:SPI 工作電源電壓:- 6 V to + 6 V |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。