- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24828 > 935268282151 (NXP SEMICONDUCTORS) 2 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP64 PDF資料下載

參數(shù)資料

| 型號: | 935268282151 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP64 |

| 封裝: | 10 X 10 MM, 1.40 MM HEIGHT, PLASTIC, MS-026, SOT-314-2, LQFP-64 |

| 文件頁數(shù): | 22/42頁 |

| 文件大小: | 218K |

| 代理商: | 935268282151 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

Philips Semiconductors

Preliminary data

PDI1394P23

2-port/1-port 400 Mbps physical layer interface

2001 Sep 06

29

subsequently interrupts the status transfer. Register contents are

considered to have been successfully transmitted only when all

8 bits of the register have been sent. A status transfer is retried after

being interrupted only if any status flags remain to be sent, or if a

register transfer has not yet completed.

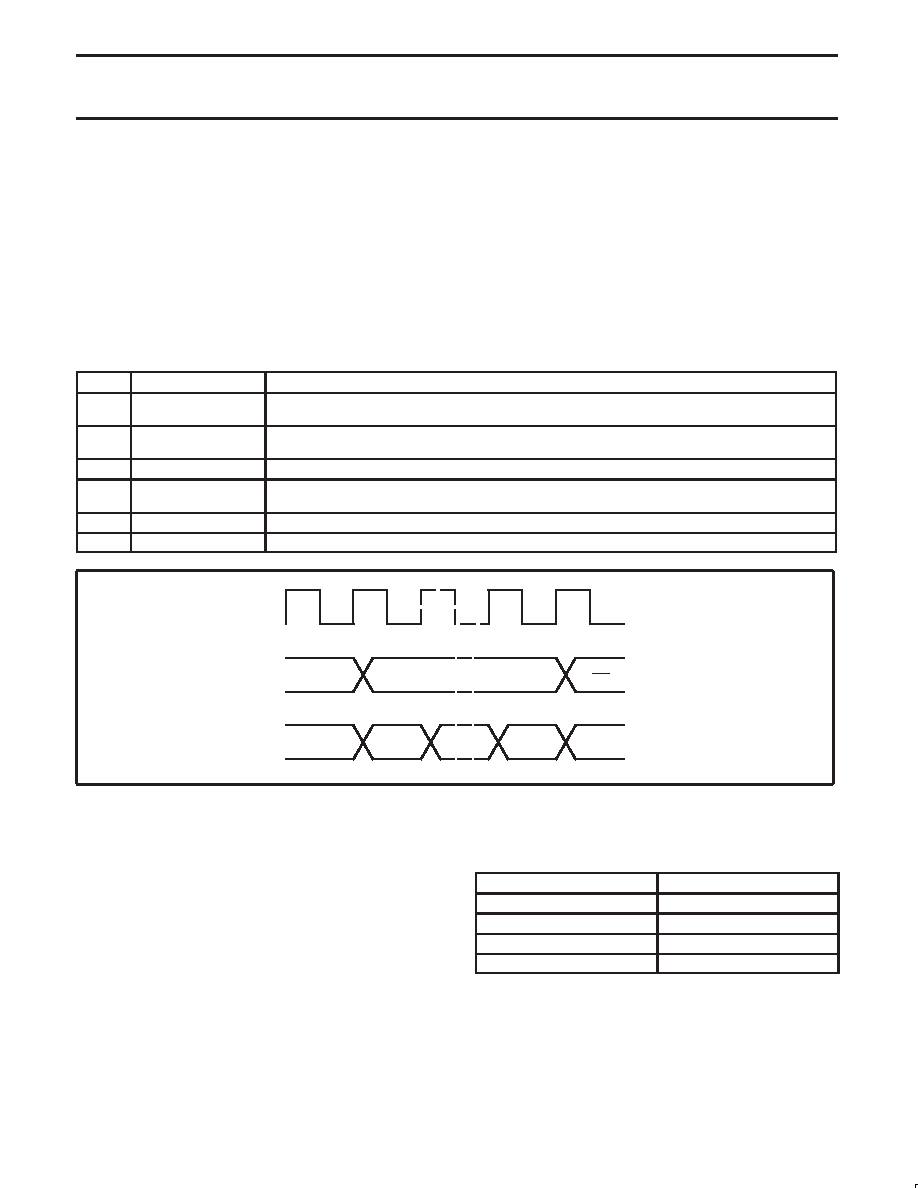

The definition of the bits in the status transfer is shown in Table 18,

and the timing is shown in Figure 15.

The sequence of events for a status transfer is as follows:

Status transfer initiated. the PHY indicates a status transfer by

asserting status on the CTL lines along with the status data on the

D0 and D1 lines (only 2 bits of status are transferred per cycle).

Normally (unless interrupted by a receive operation), a status

transfer will be either 2 or 8 cycles long. A 2-cycle (4 bit) transfer

occurs when only status information is to be sent. An 8-cycle

(16 bit) transfer occurs when register data is to be sent in addition

to any status information.

Status transfer terminated. The PHY normally terminates a status

transfer by asserting idle on the CTL lines. If a bus reset is

pending, the PHY may also assert Grant on the CTL line

immediately following a complete status transfer.

Table 18. Status Bits

BIT(S)

NAME

DESCRIPTION

0

Arbitration Reset Gap

Indicates that the PHY has detected that the bus has been idle for an arbitration reset gap time (as

defined in the IEEE 1394–1995 standard). This bit is used by the LLC in the busy/retry state machine.

1

Subaction gap

Indicates that the PHY has detected that the bus has been idle for a subaction gap time (as defined in the

IEEE 1394–1995 standard). This bit is used by the LLC to detect the completion of an isochronous cycle.

2

Bus reset

Indicates that the PHY has entered the bus reset state.

3

Interrupt

Indicates that a PHY interrupt event has occurred. An interrupt event may be a configuration time-out, a

cable-power voltage falling too low, a state time-out, or a port status change.

4–7

Address

This field holds the address of the PHY register whose contents are being transferred to the LLC.

8–15

Data

This field holds the register contents.

SYSCLK

(a)

(b)

CTL0, CTL1

D0, D1

00

01

00

01

S[14:15]

S[0:1]

SV01759

Figure 15.

Status Transfer Timing

18.3

Receive

Whenever the PHY detects the data-prefix state on the serial bus, it

initiates a receive operation by asserting Receive on the CTL terminals

and a logic 1 on each of the D terminals (“data-on” indication). The

PHY indicates the start of a packet by placing the speed code

(encoded as shown in Table 19) on the D terminals, followed by

packet data. The PHY holds the CTL terminals in the Receive state

until the last symbol of the packet has been transferred. The PHY

indicates the end of packet data by asserting Idle on the CTL

terminals. All received packets are transferred to the LLC. Note that

the speed code is part of the PHY-LLC protocol and is not included in

the calculation of CRC or any other data protection mechanisms.

Table 19. Speed Code for the Receiver

D0–D7

DATA RATE

0000 0000

S100

0100 0000

S200

0101 0000

S400

1111 1111

“data-on” indication

It is possible for the PHY to receive a null packet, which consists of

the data-prefix state on the serial bus followed by the data-end state,

相關PDF資料 |

PDF描述 |

|---|---|

| 080155R0 | TELEFON-AKKU |

| 935268378118 | LVC/LCX/Z SERIES, 2-INPUT NAND GATE, PDSO5 |

| 935268378125 | LVC/LCX/Z SERIES, 2-INPUT NAND GATE, PDSO5 |

| 935268380115 | LVC/LCX/Z SERIES, 2-INPUT AND GATE, PDSO5 |

| 935268380125 | LVC/LCX/Z SERIES, 2-INPUT AND GATE, PDSO5 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

| 935269544557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-2US1-V1.3 |

| 935269987557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-1US1-V1.8 SUBBED TO 935269987557 |

| 935270713557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC CHP |

發(fā)布緊急采購,3分鐘左右您將得到回復。