- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄296206 > 71V65703S75BGG (INTEGRATED DEVICE TECHNOLOGY INC) 256K X 36 ZBT SRAM, 7.5 ns, PBGA119 PDF資料下載

參數(shù)資料

| 型號: | 71V65703S75BGG |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | SRAM |

| 英文描述: | 256K X 36 ZBT SRAM, 7.5 ns, PBGA119 |

| 封裝: | 14 X 22 MM, GREEN, PLASTIC, MS-026AA, BGA-119 |

| 文件頁數(shù): | 6/26頁 |

| 文件大?。?/td> | 972K |

| 代理商: | 71V65703S75BGG |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁

6.42

14

IDT71V65703, IDT71V65903, 256K x 36, 512K x 18, 3.3V Synchronous ZBT SRAMs with

3.3V I/O, Burst Counter, and Flow-Through Outputs

Commercial and Industrial Temperature Ranges

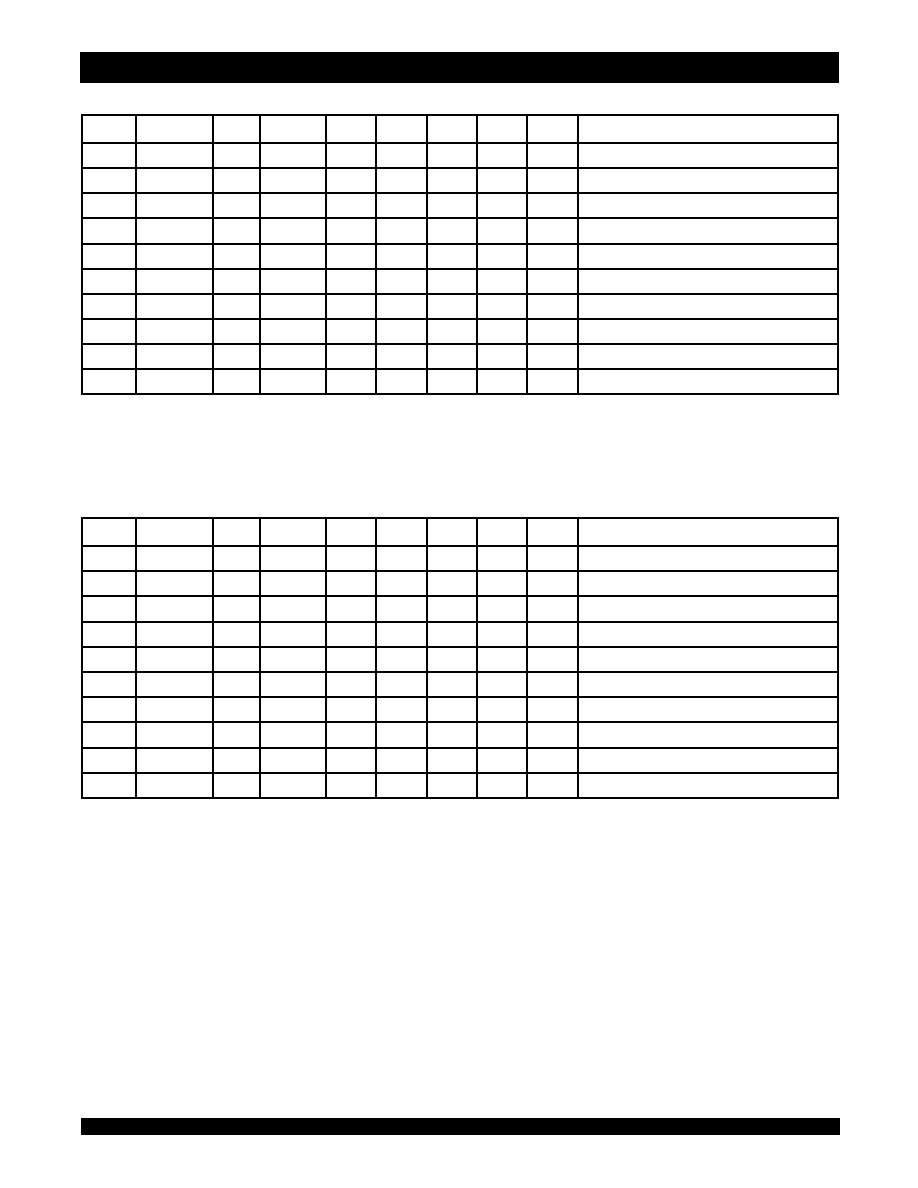

Read Operation with Chip Enable Used(1)

Write Operation with Chip Enable Used(1)

NOTES:

1. H = High; L = Low; X = Don’t Care; ? = Don’t Know; Z = High Impedance.

2.

CE2 timing transition is identical to CE1 signal. CE2 timing transition is identical but inverted to the CE1 and CE2 signals.

3. Device outputs are ensured to be in High-Z during device power-up.

NOTES:

1. H = High; L = Low; X = Don’t Care; ? = Don’t Know; Z = High Impedance.

2.

CE = L is defined as CE1 = L, CE2 = L and CE2 = H. CE = H is defined as CE1 = H, CE2 = H or CE2 = L.

Cycle

Address

R/

W

ADV/

LD

CE1(2)

CEN

BWx

OE

I/O(3)

Comments

n

X

L

H

L

X

?

Deselected.

n+1

X

L

H

L

X

Z

Deselected.

n+2

A0

H

L

X

Z

Address A0 and Control meet setup.

n+3

X

L

H

L

X

L

Q0

Address A0 read out, Deselected.

n+4

A1

H

L

X

Z

Address A1 and Control meet setup.

n+5

X

L

H

L

X

L

Q1

Address A1 read out, Deselected.

n+6

X

L

H

L

X

Z

Deselected.

n+7

A2

H

L

X

Z

Address A2 and Control meet setup.

n+8

X

L

H

L

X

L

Q2

Address A2 read out, Deselected.

n+9

X

L

H

L

X

Z

Deselected.

5298 tbl 19

Cycle

Address

R/

W

ADV

/LD

CE(2)

CEN

BWx

OE

I/O

Comments

n

X

L

H

L

X

?

Deselected.

n+1

X

L

H

L

X

Z

Deselected.

n+2

A0

L

LLL

X

Z

Address A0 and Control meet setup

n+3

X

L

H

L

X

D0

Data D0 Write In, Deselected.

n+4

A1

L

LLL

X

Z

Address A1 and Control meet setup

n+5

X

L

H

L

X

D1

Data D1 Write In, Deselected.

n+6

X

L

H

L

X

Z

Deselected.

n+7

A2

L

LLL

X

Z

Address A2 and Control meet setup

n+8

X

L

H

L

X

D2

Data D2 Write In, Deselected.

n+9

X

L

H

L

X

Z

Deselected.

5298 tbl 20

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT71V65903S80B | 512K X 18 ZBT SRAM, 8 ns, PBGA119 |

| IDT7210L25PQF | 16-BIT, DSP-MULTIPLIER ACCUMULATOR/SUMMER, PQFP64 |

| IDT7281L25SOI | 512 X 9 OTHER FIFO, 25 ns, PDSO28 |

| 7200L20TDB | 256 X 9 OTHER FIFO, 20 ns, CDIP28 |

| IDT7281L25TPI | 512 X 9 OTHER FIFO, 25 ns, PDIP28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 71V65703S75BGG8 | 功能描述:靜態(tài)隨機(jī)存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 71V65703S75BQ | 功能描述:靜態(tài)隨機(jī)存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 71V65703S75BQ8 | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Sync Single 3.3V 9M-Bit 256K x 36 7.5ns 165-Pin CABGA T/R 制造商:Integrated Device Technology Inc 功能描述:SRAM SYNC SGL 3.3V 9MBIT 256KX36 7.5NS 165FPBGA - Tape and Reel |

| 71V65703S75BQG | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Sync Single 3.3V 9M-Bit 256K x 36 7.5ns 165-Pin CABGA 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Sync Single 3.3V 9M-Bit 256K x 36 7.5ns 165-Pin CABGA Tray 制造商:Integrated Device Technology Inc 功能描述:SRAM SYNC SGL 3.3V 9MBIT 256KX36 7.5NS 165FPBGA - Rail/Tube |

| 71V65703S75BQG8 | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Sync Single 3.3V 9M-Bit 256K x 36 7.5ns 165-Pin CABGA T/R 制造商:Integrated Device Technology Inc 功能描述:SRAM SYNC SGL 3.3V 9MBIT 256KX36 7.5NS 165FPBGA - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。