- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄296206 > 71V65703S75BGG (INTEGRATED DEVICE TECHNOLOGY INC) 256K X 36 ZBT SRAM, 7.5 ns, PBGA119 PDF資料下載

參數(shù)資料

| 型號: | 71V65703S75BGG |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | SRAM |

| 英文描述: | 256K X 36 ZBT SRAM, 7.5 ns, PBGA119 |

| 封裝: | 14 X 22 MM, GREEN, PLASTIC, MS-026AA, BGA-119 |

| 文件頁數(shù): | 10/26頁 |

| 文件大小: | 972K |

| 代理商: | 71V65703S75BGG |

6.42

18

IDT71V65703, IDT71V65903, 256K x 36, 512K x 18, 3.3V Synchronous ZBT SRAMs with

3.3V I/O, Burst Counter, and Flow-Through Outputs

Commercial and Industrial Temperature Ranges

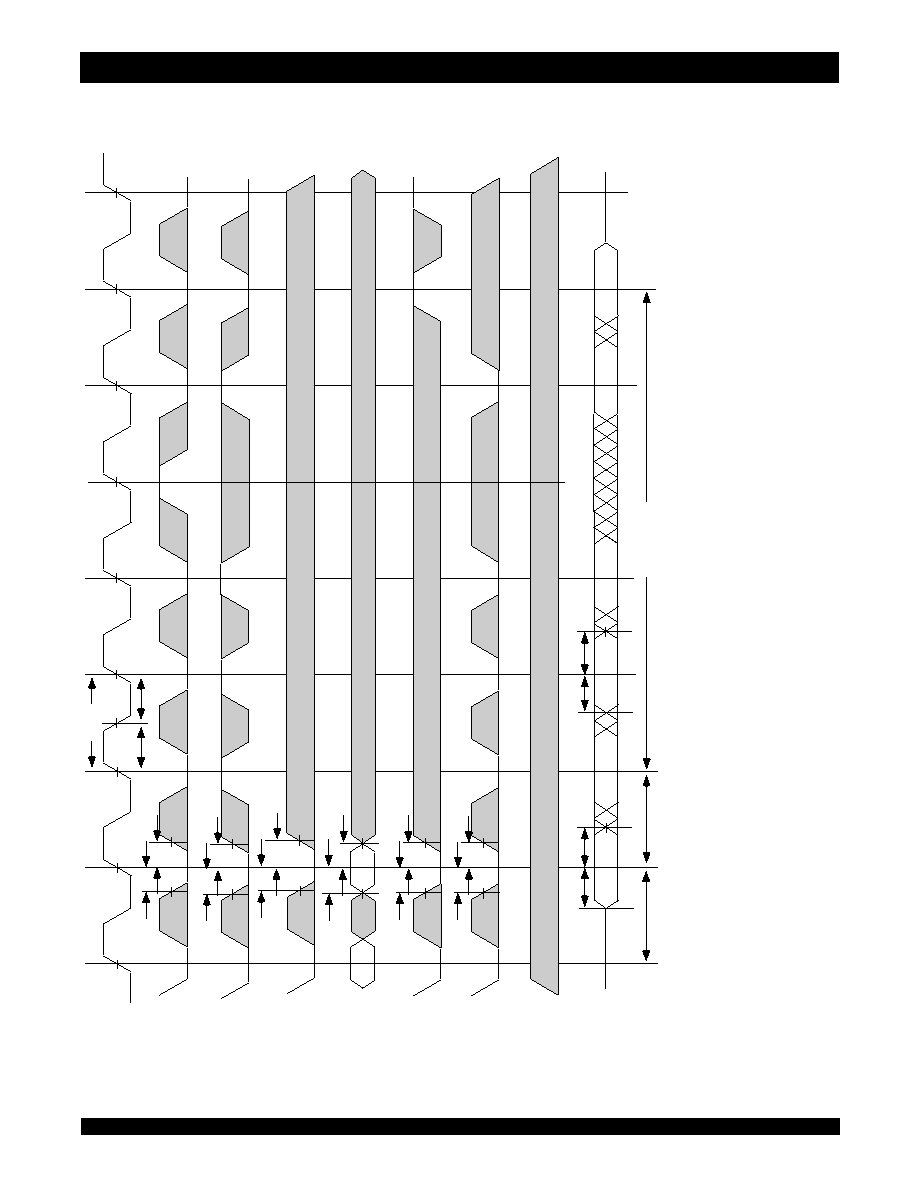

Timing Waveform of Write Cycles(1,2,3,4,5)

NOTES:

1.

D

(A

1)

represents

the

first

input

to

the

external

address

A

1.

D

(A

2)

represents

the

first

input

to

the

external

address

A

2;

D

(A

2+1

)represents

the

next

input

data

in

the

burst

sequence

of

the

base

address

A

2,

etc.

where

address

bits

A

0and

A

1are

advancing

for

the

four

word

burst

in

the

sequence

defined

by

the

state

of

the

LBO

input.

2.

CE

2timing

transitions

are

identical

but

inverted

to

the

CE

1and

CE

2

signals.

For

example,

when

CE

1and

CE

2are

LOW

on

this

waveform,

CE

2is

HIGH.

3.

Burst

ends

when

new

address

and

control

are

loaded

into

the

SRAM

by

sampling

ADV/

LD

LOW.

4.

R

/W

is

don’t

care

when

the

SRAM

is

bursting

(ADV/

LD

sampled

HIGH).

The

nature

of

the

burst

access

(Read

or

Write)

is

fixed

by

the

state

of

the

R/

W

signal

when

new

address

and

control

are

loaded

into

the

SRAM.

5.

Individual

Byte

Write

signals

(

BW

x)

must

be

valid

on

all

write

and

burst-write

cycles.

A

write

cycle

is

initiated

when

R/

W

signal

is

sampled

LOW.

The

byte

write

information

comes

in

one

cycle

before

the

actual

data

is

presented

to

the

SRAM.

tH

E

tS

E

R

/W

A

1

A

2

C

L

K

C

E

N

A

D

V

/L

D

A

D

R

E

S

C

E

1

,

C

E

2

(2

)

B

W

1

-

B

W

4

O

E

D

A

T

A

IN

D

(A

1

)

D

(A

2

)

tH

D

tS

D

(C

E

N

hi

gh,

el

im

inat

es

c

u

rrent

L

-H

cl

o

c

k

ed

ge)

D

(A

2+

1

)

D

(A

2+

2

)

D

(A

2+

3

)

D

(A

2

)

B

ur

s

t

W

ri

te

W

ri

te

W

ri

te

(B

ur

s

t

W

raps

aro

und

to

in

it

ia

l

s

ta

te

)

tH

D

tS

D

tC

H

tC

L

tC

Y

C

tH

A

D

V

tS

A

D

V

tH

W

tS

W

tH

A

tS

A

tH

C

tS

C

tH

B

tS

B

52

9

8

drw

07

B

(A

1

)

B

(A

2

)

B

(A

2+

1

)

B

(A

2+

2

)

B

(A

2+

3

)

B

(A

2

)

,

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT71V65903S80B | 512K X 18 ZBT SRAM, 8 ns, PBGA119 |

| IDT7210L25PQF | 16-BIT, DSP-MULTIPLIER ACCUMULATOR/SUMMER, PQFP64 |

| IDT7281L25SOI | 512 X 9 OTHER FIFO, 25 ns, PDSO28 |

| 7200L20TDB | 256 X 9 OTHER FIFO, 20 ns, CDIP28 |

| IDT7281L25TPI | 512 X 9 OTHER FIFO, 25 ns, PDIP28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 71V65703S75BGG8 | 功能描述:靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 71V65703S75BQ | 功能描述:靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 71V65703S75BQ8 | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Sync Single 3.3V 9M-Bit 256K x 36 7.5ns 165-Pin CABGA T/R 制造商:Integrated Device Technology Inc 功能描述:SRAM SYNC SGL 3.3V 9MBIT 256KX36 7.5NS 165FPBGA - Tape and Reel |

| 71V65703S75BQG | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Sync Single 3.3V 9M-Bit 256K x 36 7.5ns 165-Pin CABGA 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Sync Single 3.3V 9M-Bit 256K x 36 7.5ns 165-Pin CABGA Tray 制造商:Integrated Device Technology Inc 功能描述:SRAM SYNC SGL 3.3V 9MBIT 256KX36 7.5NS 165FPBGA - Rail/Tube |

| 71V65703S75BQG8 | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Sync Single 3.3V 9M-Bit 256K x 36 7.5ns 165-Pin CABGA T/R 制造商:Integrated Device Technology Inc 功能描述:SRAM SYNC SGL 3.3V 9MBIT 256KX36 7.5NS 165FPBGA - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。