- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄68811 > 71M6542F-IGTR/F (MAXIM INTEGRATED PRODUCTS INC) SPECIALTY ANALOG CIRCUIT, PQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | 71M6542F-IGTR/F |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | 模擬信號(hào)調(diào)理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 封裝: | LEAD FREE, LQFP-100 |

| 文件頁數(shù): | 99/165頁 |

| 文件大小: | 2208K |

| 代理商: | 71M6542F-IGTR/F |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁當(dāng)前第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁

v1.1

2008–2011 Teridian Semiconductor Corporation

39

Table 21: PCON Register Bit Description (SFR 0x87)

Bit

Symbol

Function

PCON[7]

SMOD

The SMOD bit doubles the baud rate when set

2.4.6

Timers and Counters

The 80515 has two 16-bit timer/counter registers: Timer 0 and Timer 1. These registers can be configured

for counter or timer operations.

In timer mode, the register is incremented every machine cycle, i.e., it counts up once for every 12 periods

of the MPU clock. In counter mode, the register is incremented when the falling edge is observed at the

corresponding input signal T0 or T1 (T0 and T1 are the timer gating inputs derived from certain DIO pins,

see 2.5.8 Digital I/O). Since it takes 2 machine cycles to recognize a 1-to-0 event, the maximum input

count rate is 1/2 of the clock frequency (CKMPU). There are no restrictions on the duty cycle, however

to ensure proper recognition of the 0 or 1 state, an input should be stable for at least 1 machine cycle.

Four operating modes can be selected for Timer 0 and Timer 1, as shown in Table 22 and Table 23. The

TMOD (SFR 0x89) Register, shown in Table 24, is used to select the appropriate mode. The timer/counter

operation is controlled by the TCON (SFR 0x88) Register, which is shown in Table 25. Bits TR1 (TCON[6])

and TR0 (TCON[4]) in the TCON register start their associated timers when set.

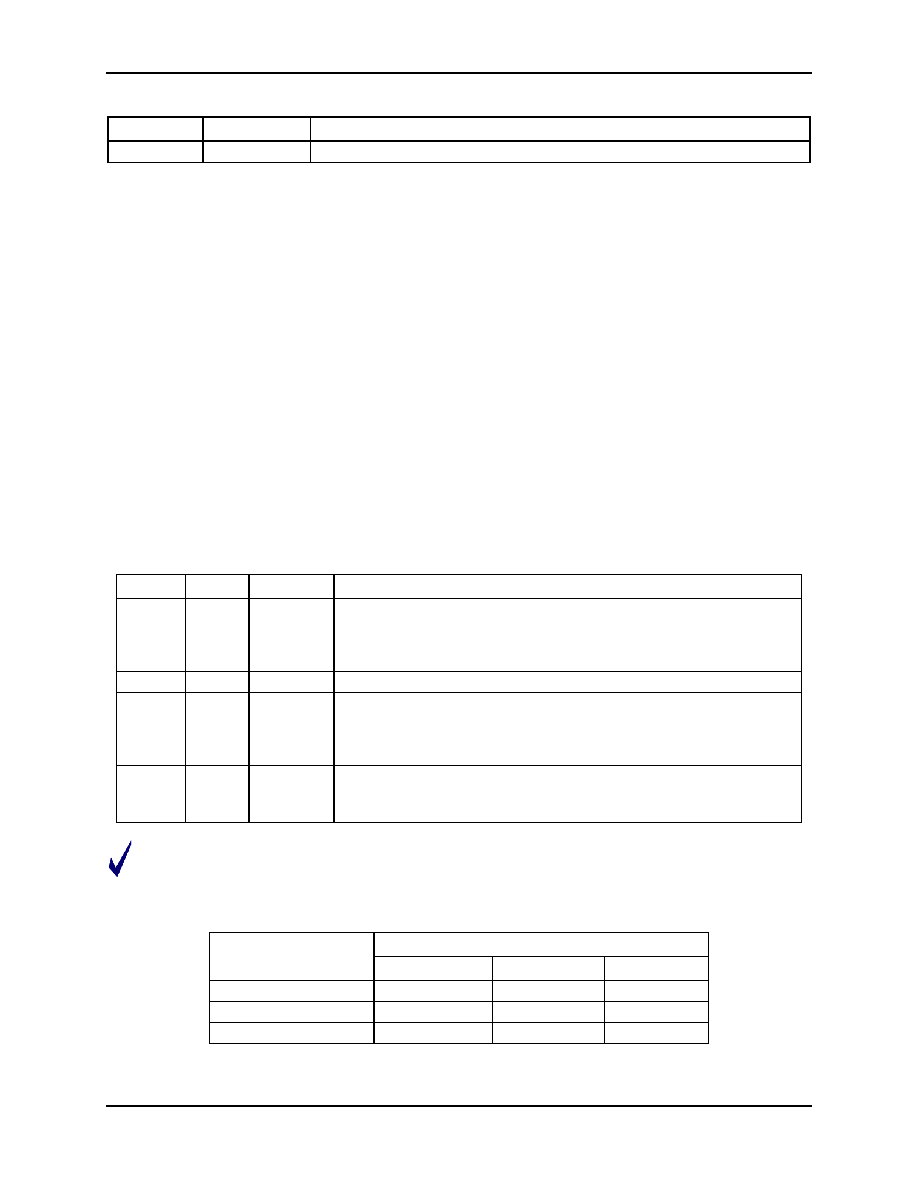

Table 22: Timers/Counters Mode Description

M1

M0

Mode

Function

0

Mode 0

13-bit Counter/Timer mode with 5 lower bits in the TL0 or TL1 (SFR

0x8A or SFR 0x8B) register and the remaining 8 bits in the TH0 or TH1

(SFR 0x8C or SFR 0x8D) register (for Timer 0 and Timer 1, respectively).

The 3 high order bits of TL0 and TL1 are held at zero.

0

1

Mode 1

16-bit Counter/Timer mode.

1

0

Mode 2

8-bit auto-reload Counter/Timer. The reload value is kept in TH0 or

TH1, while TL0 or TL1 is incremented every machine cycle. When

TL(x) overflows, a value from TH(x) is copied to TL(x) (where x is 0

for counter/timer 0 or 1 for counter/timer 1.

1

Mode 3

If Timer 1 M1 and M0 bits are set to 1, Timer 1 stops.

If Timer 0 M1 and M0 bits are set to 1, Timer 0 acts as two independent

8-bit Timer/Counters.

In Mode 3, TL0 is affected by TR0 and gate control bits, and sets the TF0 flag on overflow, while TH0

is affected by the TR1 bit, and the TF1 flag is set on overflow.

Table 23 specifies the combinations of operation modes allowed for Timer 0 and Timer 1.

Table 23: Allowed Timer/Counter Mode Combinations

Timer 1

Mode 0

Mode 1

Mode 2

Timer 0 - mode 0

Yes

Timer 0 - mode 1

Yes

Timer 0 - mode 2

Not allowed

Yes

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 71M6541D-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP64 |

| 71M6542G-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6541G-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP64 |

| 71M6541F-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP64 |

| 71M6543F-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 71M6542FT-IGT/F | 制造商:Maxim Integrated Products 功能描述:1-PHASE SOC 128KB WITH PREC TEMP SENSOR - Rail/Tube |

| 71M6542FT-IGTR/F | 制造商:Maxim Integrated Products 功能描述:1-PHASE SOC, 64KB FLASH, PRES TEMP SENSOR - Tape and Reel |

| 71M6542G | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:71M6541D/71M6541F/71M6541G/71M6542F/71M6542G 是 TeridianTM 的第4 代高集成度單相電表SoC |

| 71M6542G-IGT/F | 功能描述:計(jì)量片上系統(tǒng) - SoC 1-Phase Metering SOC with 128KB Flash RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 處理器系列:71M6511 類型:Metering SoC 最大時(shí)鐘頻率:70 Hz 程序存儲(chǔ)器大小:64 KB 數(shù)據(jù) RAM 大小:7 KB 接口類型:UART 可編程輸入/輸出端數(shù)量:12 片上 ADC: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:LQFP-64 封裝:Reel |

| 71M6542G-IGTR/F | 制造商:Maxim Integrated Products 功能描述:- Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。