- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373786 > ZL50212 (Zarlink Semiconductor Inc.) 288 Channel Voice Echo Canceller PDF資料下載

參數(shù)資料

| 型號: | ZL50212 |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | 288 Channel Voice Echo Canceller |

| 中文描述: | 288頻道語音回聲消除器 |

| 文件頁數(shù): | 29/43頁 |

| 文件大小: | 2166K |

| 代理商: | ZL50212 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁

Data Sheet

ZL50212

29

Zarlink Semiconductor Inc.

Note: In order to correctly write to Control Register 1 and 2 of ECB, it is necessary to write the data twice to the register, one

immediately after another. The two writes must be separated by at least 350ns and no more than 20us.

Power-up

00

hex

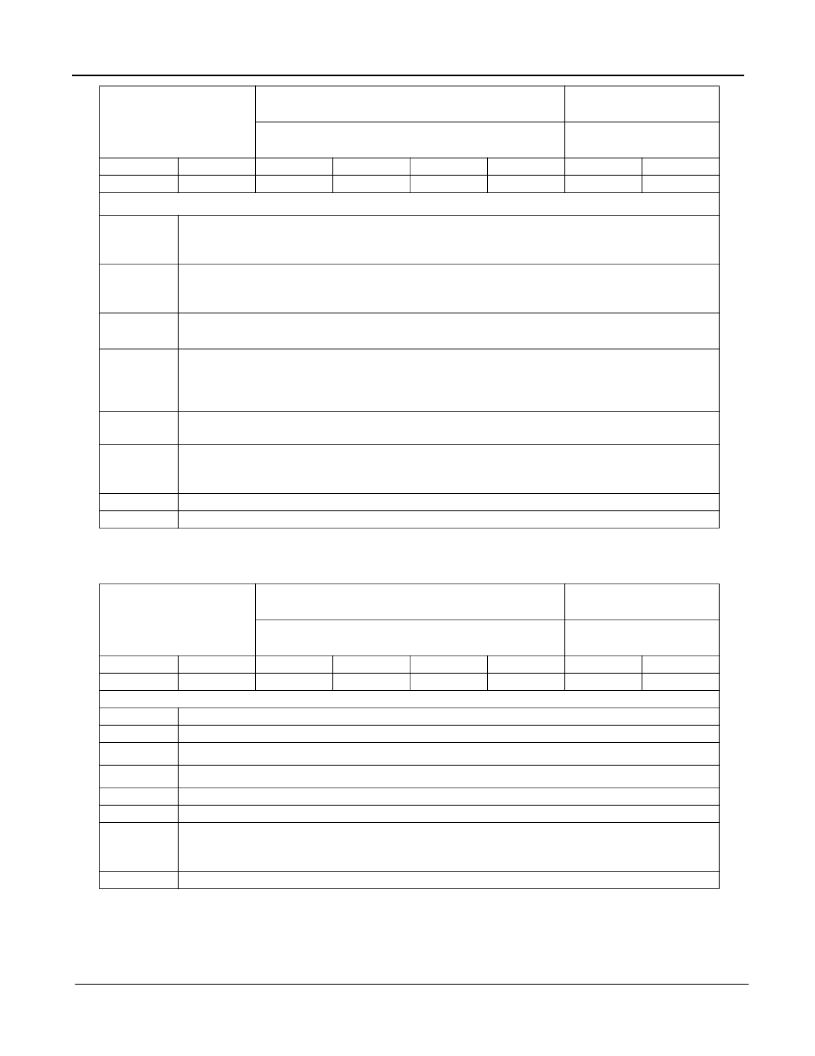

ECA: Control Register 2

R/W Address:

01

hex

+ Base Address

R/W Address:

21

hex

+ Base Address

Bit 1

MuteS

ECB: Control Register 2

Bit 7

TDis

Bit 6

PHDis

Bit 5

NLPDis

Functional Description of Register Bits

When high, tone detection is disabled. When low, tone detection is enabled. When both

Echo Cancellers A and B TDis bits are high, Tone Disable processors are disabled

entirely and are put into Power Down mode.

When high, the tone detectors will trigger upon the presence of a 2100 Hz tone regardless

of the presence/absence of periodic phase reversals. When low, the tone detectors will

trigger only upon the presence of a 2100 Hz tone with periodic phase reversals.

When high, the non-linear processor is disabled. When low, the non-linear processors

function normally. Useful for G.165 conformance testing.

Bit 4

AutoTD

Bit 3

NBDis

Bit 2

HPFDis

Bit 0

MuteR

TDis

PHDis

NLPDis

AutoTD

When high, the echo canceller puts itself in Bypass mode when the tone detectors detect

the presence of 2100 Hz tone. See PHDis for qualification of 2100 Hz tones.

When low, the echo canceller algorithm will remain operational regardless of the state of

the 2100 Hz tone detectors.

When high, the narrow-band detector is disabled. When low, the narrow-band detector is

enabled.

When high, the offset nulling high pass filters are bypassed in the Rin and Sin paths.

When low, the offset nulling filters are active and will remove DC offsets on PCM input

signals.

When high, data on Sout is muted to quiet code. When low, Sout carries active code.

When high, data on Rout is muted to quiet code. When low, Rout carries active code.

NBDis

HPFDis

MuteS

MuteR

Power-up

00

hex

ECA: Status Register

R/W Address:

02

hex

+ Base Address

R/W Address:

22

hex

+ Base Address

Bit 1

TDG

ECB: Status Register

Bit 7

Reserve

Bit 6

TD

Bit 5

DTDet

Functional Description of Register Bits

Bit 4

Reserve

Bit 3

Reserve

Bit 2

Reserve

Bit 0

NB

Reserve

TD

DTDet

Reserved bit.

Logic high indicates the presence of a 2100Hz tone.

Logic high indicates the presence of a double-talk condition.

Reserve

Reserved bit.

Reserved bit.

Reserved bit.

Tone detection status bit gated with the AutoTD bit (Control Register 2).

Logic high indicates that AutoTD has been enabled and the tone detector has detected

the presence of a 2100Hz tone.

Logic high indicates the presence of a narrow-band signal on Rin.

Reserve

Reserve

TDG

NB

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL50232GDC | 32 Channel Voice Echo Canceller |

| ZL50232QCC | Aluminum Electrolytic Capacitor; Capacitor Type:General Purpose; Voltage Rating:35VDC; Capacitor Dielectric Material:Aluminum Electrolytic; Operating Temperature Range:-40 C to +85 C; Capacitance:47uF RoHS Compliant: Yes |

| ZL50232QCC1 | 32 Channel Voice Echo Canceller |

| ZL50232 | 32 Channel Voice Echo Canceller |

| ZL50233GD | 4 Channel Voice Echo Cancellor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL50212/GBC | 制造商:Microsemi Corporation 功能描述:ECHO CANCELLER CHIP 288CH G.164/G.165/G.168/G.711 W/ TONE DE - Trays |

| ZL50212GB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecomm/Datacomm |

| ZL50232 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:32 Channel Voice Echo Canceller |

| ZL50232/GDC | 制造商:Microsemi Corporation 功能描述:ECHO CANCELLER CHIP 32CH G.164/G.165/G.168/G.711 W/ TONE DET - Trays |

| ZL50232/QCC | 制造商:Microsemi Corporation 功能描述:ECHO CANCELLER CHIP 32CH G.164/G.165/G.168/G.711 W/ TONE DET - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。