- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373786 > ZL50117 (Zarlink Semiconductor Inc.) 32, 64 and 128 Channel CESoP Processors PDF資料下載

參數(shù)資料

| 型號(hào): | ZL50117 |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | 32, 64 and 128 Channel CESoP Processors |

| 中文描述: | 32,64和128頻道CESoP處理器 |

| 文件頁(yè)數(shù): | 56/95頁(yè) |

| 文件大小: | 1157K |

| 代理商: | ZL50117 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)當(dāng)前第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)

ZL50115/16/17/18/19/20

Data Sheet

56

Zarlink Semiconductor Inc.

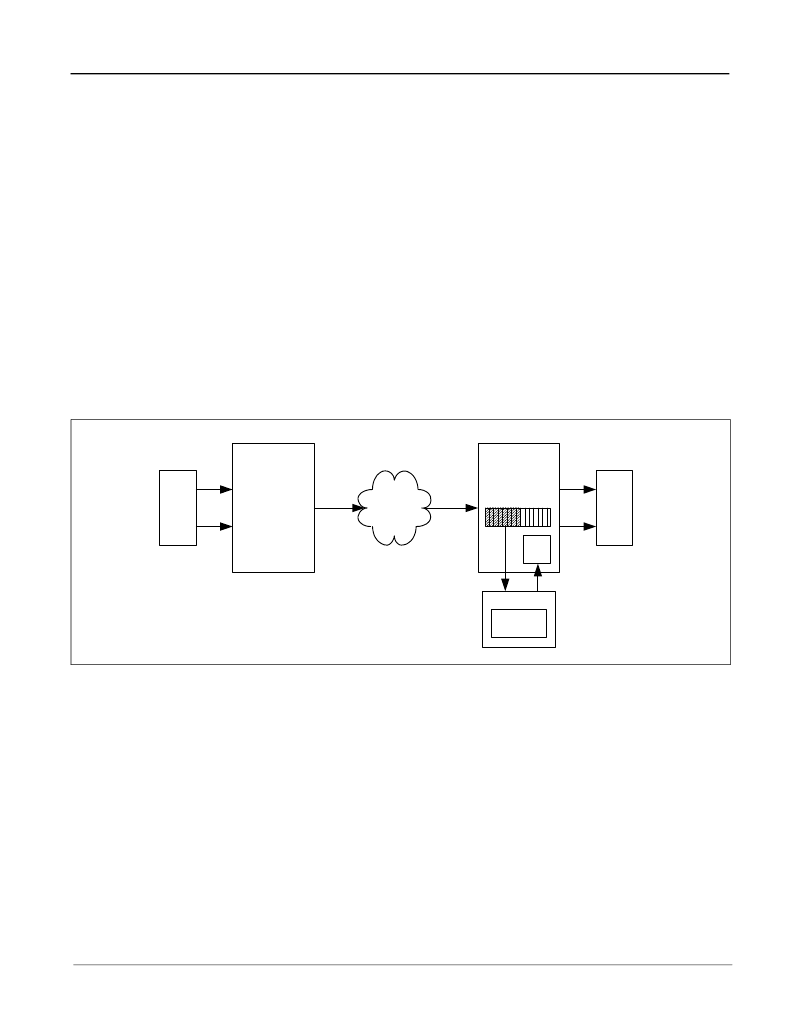

7.2 Adaptive Clock Recovery

For applications where there is no common reference clock between provider edge units, an adaptive clock

recovery technique is provided. This infers the clock rate of the original TDM service clock from the mean arrival

rate of packets at the packet egress point.

The disadvantage of this type of scheme is that, depending on the characteristics of the packet network, it may

prove difficult to regenerate a clock that stays within the wander requirements of the plesiochronous digital

hierarchy (specifically MTIE). The reason for this is that any variation in delay between packets will feed through as

a variation in the frequency of the recovered clock. High frequency jitter can be filtered out, but any low frequency

variation or wander is more difficult to remove without a very long time constant. This will in turn affect the ability of

the system to lock to the original clock within an acceptable time.

With no PRS clock the only information available to determine the TDM transmission speed is the average arrival

rate of the packets, as shown in Figure 21. Timestamps representing the number of elapsed source clock periods

may be included in the packet header, or information can be inferred from a known payload size at the destination.

It is possible to maintain average buffer-fill levels at the destination, where an increase or decrease in the fill level of

the buffer would require a change in transmission clock speed to maintain the average. Additionally, the buffer-fill

depth can be altered independently, with no relation to the recovered clock frequency, to control TDM transmission

latency.

Figure 21 - Adaptive Clock Recovery

8.0 System Features

8.1 Latency

The following lists the intrinsic processing latency of the ZL5011x. The intrinsic processing latency is dependent on

the number of channels in a context for structured operation, as detailed below. However, the intrinsic processing

latency is not dependent on the total number of contexts opened or the total number of channels being processed

by the device.

TDM to Packet transmission processing latency less than 125

μ

s

Packet to TDM transmission processing latency less than 250

μ

s (unstructured)

Packet to TDM transmission processing latency less than 250

μ

s (structured, more than 16 channels in

context)

Packet to TDM transmission processing latency less than 375

μ

s (structured, 16 or less channels in context)

LIU

LIU

ZL5011x

source

node

ZL5011x

destination

node

Host CPU

Queue

monitor

DCO

Data

Source

Clock

Data

Dest'n

Clock

Packets

Packets

Network

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL50118 | 32, 64 and 128 Channel CESoP Processors |

| ZL50119 | 32, 64 and 128 Channel CESoP Processors |

| ZL50120 | 32, 64 and 128 Channel CESoP Processors |

| ZL50115GAG | 32, 64 and 128 Channel CESoP Processors |

| ZL50116GAG | 32, 64 and 128 Channel CESoP Processors |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL50117_06 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:32, 64 and 128 Channel CESoP Processors |

| ZL50117GAG | 制造商:Microsemi Corporation 功能描述:4 TDM + 1 ETHERNET - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC CESOP PROCESSOR 128CH 324PBGA 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 128CH 324PBGA |

| ZL50117GAG2 | 制造商:Microsemi Corporation 功能描述:PB FREE 4 TDM + 1 ETHERNET - Trays 制造商:Microsemi Corporation 功能描述:PB FREE 4TDM PLUS 1 ETHERNET 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC CESOP PROCESSOR 128CH 324PBGA 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 128CH 324PBGA |

| ZL50118 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:32, 64 and 128 Channel CESoP Processors |

| ZL50118GAG | 制造商:Microsemi Corporation 功能描述:CH CESOP PROCESSORS 324BGA - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC CESOP PROCESSOR 32CH 324PBGA 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 32CH 324PBGA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。