- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16820 > XR17V358IB-E8-EVB (Exar Corporation)EVAL BOARD FOR XR17V358-E8 PDF資料下載

參數(shù)資料

| 型號: | XR17V358IB-E8-EVB |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 1/68頁 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR XR17V358-E8 |

| 產(chǎn)品培訓(xùn)模塊: | PCIe UARTs UART Product Overview |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 主要目的: | 接口,UART |

| 嵌入式: | 否 |

| 已用 IC / 零件: | XR17V358 |

| 已供物品: | 板 |

| 相關(guān)產(chǎn)品: | 1016-1294-ND - IC UART PCIE OCTAL 176FPBGA |

| 其它名稱: | 1016-1296 |

當(dāng)前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

Exar Corporation 48720 Kato Road, Fremont CA, 94538 (510) 668-7000 FAX (510) 668-7017 www.exar.com

XR17V358

HIGH PERFORMANCE OCTAL PCI EXPRESS UART

APRIL 2012

REV. 1.0.4

GENERAL DESCRIPTION

The XR17V3581 (V358) is a single chip 8-channel

PCI Express (PCIe) UART (Universal Asynchronous

Receiver and Transmitter), optimized for higher

performance and lower power. The V358 serves as a

single lane PCIe bridge to 8 indepedent enhanced

16550 compatible UARTs. The V358 is compliant to

PCIe 2.0 Gen 1 (2.5GT/s).

In addition to the UART channels, the V358 has 16

multi-purpose I/Os (MPIOs), a 16-bit general purpose

counter/timer and a global interrupt status register to

optimize interrupt servicing.

Each UART of the V358 has many enhanced

features such as the 256-bytes TX and RX FIFOs,

programmable Fractional Baud Rate Generator,

Automatic Hardware or Software Flow Control, Auto

RS-485 Half-Duplex Direction Control, programmable

TX and RX FIFO Trigger Levels, TX and RX FIFO

Level Counters, infrared mode, and data rates up to

25Mbps. The V358 is available in a 176-pin FPBGA

package (13 x 13 mm).

NOTE 1: Covered by U.S. Patents #5,649,122, #6,754,839,

#6,865,626 and #6,947,999

APPLICATIONS

Next generation Point-of-Sale Systems

Remote Access Servers

Storage Network Management

Factory Automation and Process Control

Multi-port RS-232/RS-422/RS-485 Cards

FEATURES

Single 3.3V power supply

Internal buck regulator for 1.2V core

PCIe 2.0 Gen 1 compliant

x1 Link, dual simplex, 2.5Gbps in each direction

Expansion bus interface

EEPROM interface for configuration

Global interrupt status register for all eight UARTs

Up to 25 Mbps serial data rate

16 multi-purpose inputs/outputs (MPIOs)

16-bit general purpose timer/counter

Sleep mode with wake-up Indicator

Eight independent UART channels controlled with

■

16550 compatible register Set

■

256-byte TX and RX FIFOs

■

Programmable TX and RX Trigger Levels

■

TX/RX FIFO Level Counters

■

Fractional baud rate generator

■

Automatic RTS/CTS or DTR/DSR hardware

flow control with programmable hysteresis

■

Automatic Xon/Xoff software flow control

■

RS-485 half duplex direction control output

with programmable turn-around delay

■

Multi-drop with Auto Address Detection

■

Infrared (IrDA 1.1) data encoder/decoder

Software compatible to XR17C15x, XR17D15x,

XR17V25x PCI UARTs

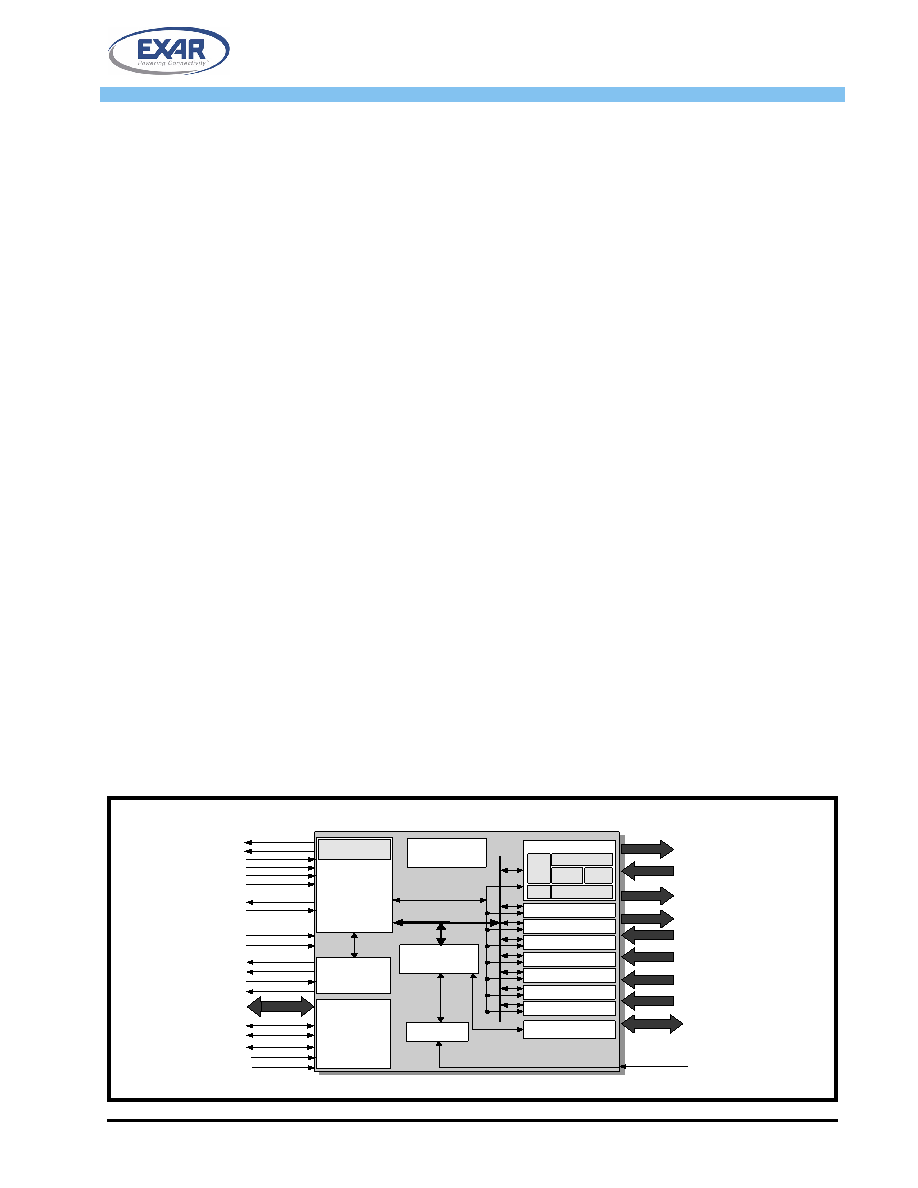

FIGURE 1. BLOCK DIAGRAM OF THE XR17V358

G loba l

C onfigur a tion

R eg ister s

C r ystal O s c/B u ffer

P C I L o cal

Bu s

In te r fa c e

C o nfigur a tion

Sp a c e

R eg ister s

M ulti- pur pos e

In puts /O utputs

16 - b it

Tim e r/C ounte r

UA RT Ch a n n e l 0

6 4 - b y te TX FIFO

6 4 - by te R X F IFO

BR G

IR

E NDE C

T X & RX

U ART

Re g s

TX +

RX +

EE C K

EE D O

EE C S

UA RT Ch a n n e l 1

UA RT Ch a n n e l 2

UA RT Ch a n n e l 3

UA RT Ch a n n e l 4

UA RT Ch a n n e l 5

UA RT Ch a n n e l 6

UA RT Ch a n n e l 7

TM R C K

RX[7 :0 ]

T X [7 :0 ]

RT S # [7 :0 ]

DT R# [7 :0 ]

C T S # [7 :0 ]

D S R # [7 :0 ]

D C D #[7 :0]

M P IO [7 :0 ]

R I#[7 :0]

EE PRO M

In ter face

G loba l

C onfigur a tion

R eg ister s

G loba l

C onfigur a tion

R eg ister s

PCIe

In ter face

C o nfigur a tion

Sp a c e

R eg ister s

M ulti- pur pos e

In puts /O utputs

M ulti-pur pos e

In puts /O utputs

16 - b it

Tim e r/C ounte r

16 - b it

Tim e r/C ounte r

UA RT Ch a n n e l 0

6 4 - b y te TX FIFO

64-

BR G

IR

E NDE C

T X & RX

U ART

Re g s

UA RT Ch a n n e l 0

256-b yte T X F IF O

BR G

IR

E NDE C

TX & R X

U ART

Re g s

EE D I

UA RT Ch a n n e l 1

UA RT Ch a n n e l 2

UA RT Ch a n n e l 3

UA RT Ch a n n e l 4

UA RT Ch a n n e l 5

UA RT Ch a n n e l 6

UA RT Ch a n n e l 7

TM R C K

R X [7 :0 ]

T X [7 :0 ]

RT S # [7 :0 ]

DT R # [7 :0 ]

C T S # [7 :0 ]

D S R # [7 :0 ]

D C D #[7 :0]

M P IO [7 :0 ]

MP IO [1 5 :0 ]

R I#[7 :0]

EN IR #

EE PRO M

In ter face

EE PRO M

In ter face

256-b y te R X F IF O

TX -

RX -

CL K+

CL K-

CL KRE Q #

PE R S T #

E N 485#

E x pa ns ion

In te rfa c e

D[7 :0 ]

SE L

IN T

MO D E

CL K

B uc k R e gula tor

125 M H z C lo ck

PR E S

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EBM24DCSH-S288 | CONN EDGECARD 48POS .156 EXTEND |

| EGM08DRST | CONN EDGECARD 16POS DIP .156 SLD |

| V150B28E150BL | CONVERTER MOD DC/DC 28V 150W |

| HSM06DRYH-S13 | CONN EDGECARD 12POS .156 EXTEND |

| EBM24DCSD-S288 | CONN EDGECARD 48POS .156 EXTEND |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR1857SN | 制造商:Electro-Term/Hollingsworth 功能描述: |

| XR1858SN | 制造商:Electro-Term/Hollingsworth 功能描述: |

| XR1859SN | 制造商:Electro-Term/Hollingsworth 功能描述: |

| XR1859SNT | 制造商:Hollingsworth 功能描述: |

| XR1880S | 制造商:Electro-Term/Hollingsworth 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。