- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄3985 > XCS30-4VQ100C (Xilinx Inc)IC FPGA 5V C-TEMP 100-VQFP PDF資料下載

參數(shù)資料

| 型號: | XCS30-4VQ100C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 35/83頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA 5V C-TEMP 100-VQFP |

| 標準包裝: | 90 |

| 系列: | Spartan® |

| LAB/CLB數(shù): | 576 |

| 邏輯元件/單元數(shù): | 1368 |

| RAM 位總計: | 18432 |

| 輸入/輸出數(shù): | 77 |

| 門數(shù): | 30000 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 100-TQFP |

| 供應商設備封裝: | 100-VQFP(14x14) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當前第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁

Spartan and Spartan-XL FPGA Families Data Sheet

40

DS060 (v2.0) March 1, 2013

Product Specification

R

Product Obsolete/Under Obsolescence

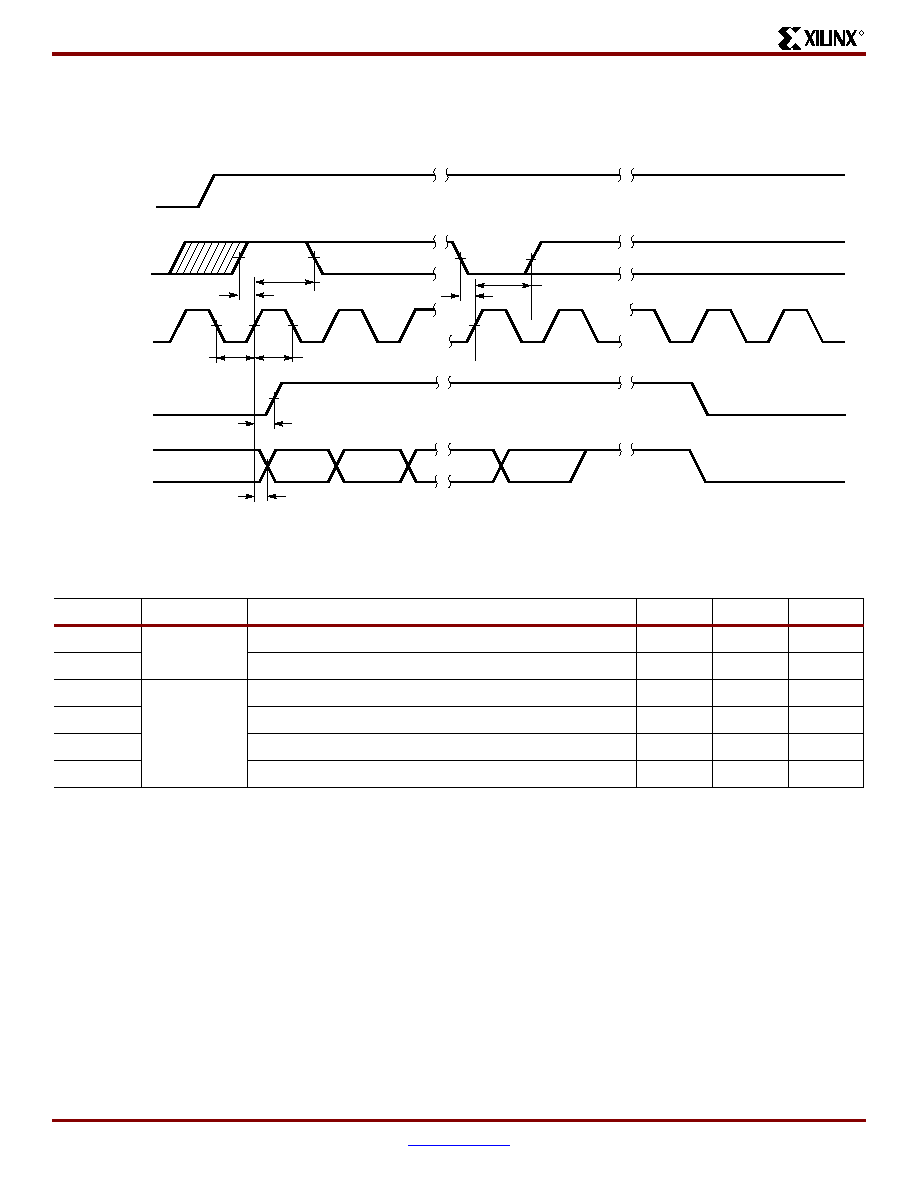

Readback Switching Characteristics Guidelines

The following guidelines reflect worst-case values over the

recommended operating conditions.

Figure 33: Spartan and Spartan-XL Readback Timing Diagram

Spartan and Spartan-XL Readback Switching Characteristics

Symbol

Description

Min

Max

Units

TRTRC

rdbk.TRIG

rdbk.TRIG setup to initiate and abort Readback

200

-

ns

TRCRT

rdbk.TRIG hold to initiate and abort Readback

50

-

ns

TRCRD

rdclk.I

rdbk.DATA delay

-

250

ns

TRCRR

rdbk.RIP delay

-

250

ns

TRCH

High time

250

500

ns

TRCL

Low time

250

500

ns

Notes:

1.

Timing parameters apply to all speed grades.

2.

If rdbk.TRIG is High prior to Finished, Finished will trigger the first Readback.

TRTRC

TRCRT

TRCH

TRCRR

TRCRD

TRTRC

TRCRT

TRCL

DUMMY

rdbk.DATA

rdbk.RIP

rdclk.I

rdbk.TRIG

Finished

Internal Net

VALID

DS060_32_080400

VALID

相關PDF資料 |

PDF描述 |

|---|---|

| 1-1734248-9 | CONN FPC/ZIP 19POS 1MM VERT SMD |

| KMPC860ENVR66D4 | IC MPU POWERQUICC 66MHZ 357-PBGA |

| AMC31DTEH | CONN EDGECARD 62POS .100 EYELET |

| KMPC860ENCZQ66D4 | IC MPU POWERQUICC 66MHZ 357-PBGA |

| IDT7015L17G | IC SRAM 72KBIT 17NS 68PGA |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XCS30-4VQ100I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS30-4VQ144C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS30-4VQ144I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS30-4VQ208C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS30-4VQ208I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復。