- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372880 > XCCACEM32SERIES System ACE MPM Solution PDF資料下載

參數(shù)資料

| 型號: | XCCACEM32SERIES |

| 英文描述: | System ACE MPM Solution |

| 中文描述: | 系統(tǒng)ACE MPM的解決方案 |

| 文件頁數(shù): | 6/29頁 |

| 文件大?。?/td> | 285K |

| 代理商: | XCCACEM32SERIES |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁

R

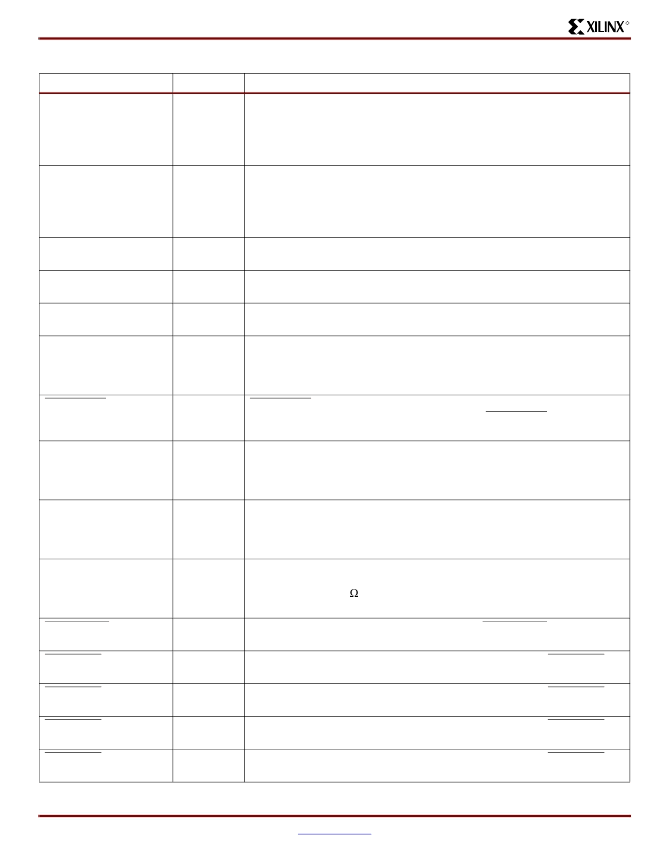

Pin Name

Pin Type

Description

CFG_DATA[6]

Output

For Slave-Serial configuration mode, CFG_DATA[6] is the serial data signal for

Serial-Slave Chain 6 and is connected to DIN of the first FPGA in the

Slave-Serial Chain 6. For Slave-SelectMAP configuration mode, CFG_DATA[6]

is the data bit 6 on the SelectMAP bus and is connected to D6 on all target

FPGAs.

CFG_DATA[7]

Output

For Slave-Serial configuration mode, CFG_DATA[7] is the serial data signal for

Serial-Slave Chain 7 and is connected to DIN of the first FPGA in the

Slave-Serial Chain 7. For Slave-SelectMAP configuration mode, CFG_DATA[7]

is the data bit 7 on the SelectMAP bus and is connected to D7 on all target

FPGAs.

CFG_MODE[0]

Output

The CFG_MODE pins set the configuration mode on the target FPGAs.

Connect CFG_MODE[0] to the M0 pin on all target FPGAs.

CFG_MODE[1]

Output

The CFG_MODE pins set the configuration mode on the target FPGAs.

Connect CFG_MODE[1] to the M1 pin on all target FPGAs.

CFG_MODE[2]

Output

The CFG_MODE pins set the configuration mode on the target FPGAs.

Connect CFG_MODE[2] to the M2 pin on all target FPGAs.

CFG_CCLK

Output

CFG_CCLK is the configuration clock source for the target FPGAs. The

CFG_CCLK is derived from the SYSCLK. The CFG_CCLK frequency is half

the SYSCLK frequency. Connect CFG_CCLK to the CCLK pin on all target

FPGAs.

CFG_PROG

Output

CFG_PROG is pulsed Low at the beginning of the configuration download to

reset the configuration state of the target FPGAs. CFG_PROG is connected to

the PROG_B pin on all target FPGAs.

CFG_INIT

Input

Target FPGA INIT monitor pin. At the start of the configuration process, the

System ACE MPM controller waits for INIT to go High before initiating delivery

of configuration data through the CFG_DATA pins. CFG_INIT is connected to

the INIT pin on all target FPGAs.

CFG_BUSY

Input

When CFG_BUSY is High, the CFG_DATA outputs are held. If the target FPGA

configuration mode is Slave-SelectMAP and if the CFG_CCLK is greater than

50 MHz, connect the CFG_BUSY pin to the BUSY pin on all target FPGAs.

Otherwise, pull-down the CFG_BUSY pin to GND.

CFG_DONE

Input

CFG_DONE monitors the DONE status on all target FPGAs. Connect the

CFG_DONE to the DONE pin on all target FPGAs. DONE must be pulled High

with an external 330-

8

pull-up resistor. The BitGen option DriveDONE should

be left in the default

“

NO

”

setting when generating bitstreams for Xilinx FPGAs.

CFG_WRITE

Output

Slave-SelectMAP write-enable pin. Connect the CFG_WRITE pin to the

RDWR_B pin on all target FPGAs.

CFG_CS[0]

Output

Slave-SelectMAP chip-enable for target FPGA 0. Connect the CFG_CS[0] pin

to the CS_B pin on target FPGA 0.

CFG_CS[1]

Output

Slave-SelectMAP chip-enable for target FPGA 1. Connect the CFG_CS[1] pin

to the CS_B pin on target FPGA 1.

CFG_CS[2]

Output

Slave-SelectMAP chip-enable for target FPGA 2. Connect the CFG_CS[2] pin

to the CS_B pin on target FPGA 2.

CFG_CS[3]

Output

Slave-SelectMAP chip-enable for target FPGA 3. Connect the CFG_CS[3] pin

to the CS_B pin on target FPGA 3.

Table 3:

Target FPGA Configuration Pins

(Continued)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XCCACEM64SERIES | System ACE MPM Solution |

| XCCACESERIES | System ACE CompactFlash Solution |

| XCD3558 | GEWINDELOCHBOHRER HEXIBIT M3.5 M5 M8 |

| XCD358 | GEWINDELOCHBOHRER HEXIBIT M3 M5 M8 |

| XCD4610 | GEWINDELOCHBOHRER HEXIBIT M4 M6 M10 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCCACEM64BG388I | 制造商:XILINX 制造商全稱:XILINX 功能描述:System ACE MPM Solution |

| XCCACEM64-BG388I | 功能描述:SYS ACE MULTIPKG MODULE 64MBIT RoHS:否 類別:存儲卡,模塊 >> 存儲器 - 模塊 系列:- 標(biāo)準(zhǔn)包裝:100 系列:- 存儲器類型:SDRAM 存儲容量:1GB 速度:133MHz 特點(diǎn):- 封裝/外殼:168-DIMM |

| XCCACEM64SERIES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:System ACE MPM Solution |

| XCCACESERIES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:System ACE CompactFlash Solution |

| XCCACE-TQ144 | 制造商:XILINX 制造商全稱:XILINX 功能描述:System ACE CompactFlash Solution |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。