- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4214 > XC6VCX130T-2FFG784I (Xilinx Inc)IC FPGA VIRTEX 6 128K 784FFGBGA PDF資料下載

參數(shù)資料

| 型號(hào): | XC6VCX130T-2FFG784I |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 42/52頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA VIRTEX 6 128K 784FFGBGA |

| 產(chǎn)品培訓(xùn)模塊: | Virtex-6 FPGA Overview |

| 產(chǎn)品變化通告: | Virtex-6 FIFO Input Logic Reset 18/Apr/2011 |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | Virtex® 6 CXT |

| LAB/CLB數(shù): | 10000 |

| 邏輯元件/單元數(shù): | 128000 |

| RAM 位總計(jì): | 9732096 |

| 輸入/輸出數(shù): | 400 |

| 電源電壓: | 0.95 V ~ 1.05 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 784-BBGA,F(xiàn)CBGA |

| 供應(yīng)商設(shè)備封裝: | 784-FCBGA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)當(dāng)前第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)

Virtex-6 CXT Family Data Sheet

DS153 (v1.6) February 11, 2011

Product Specification

47

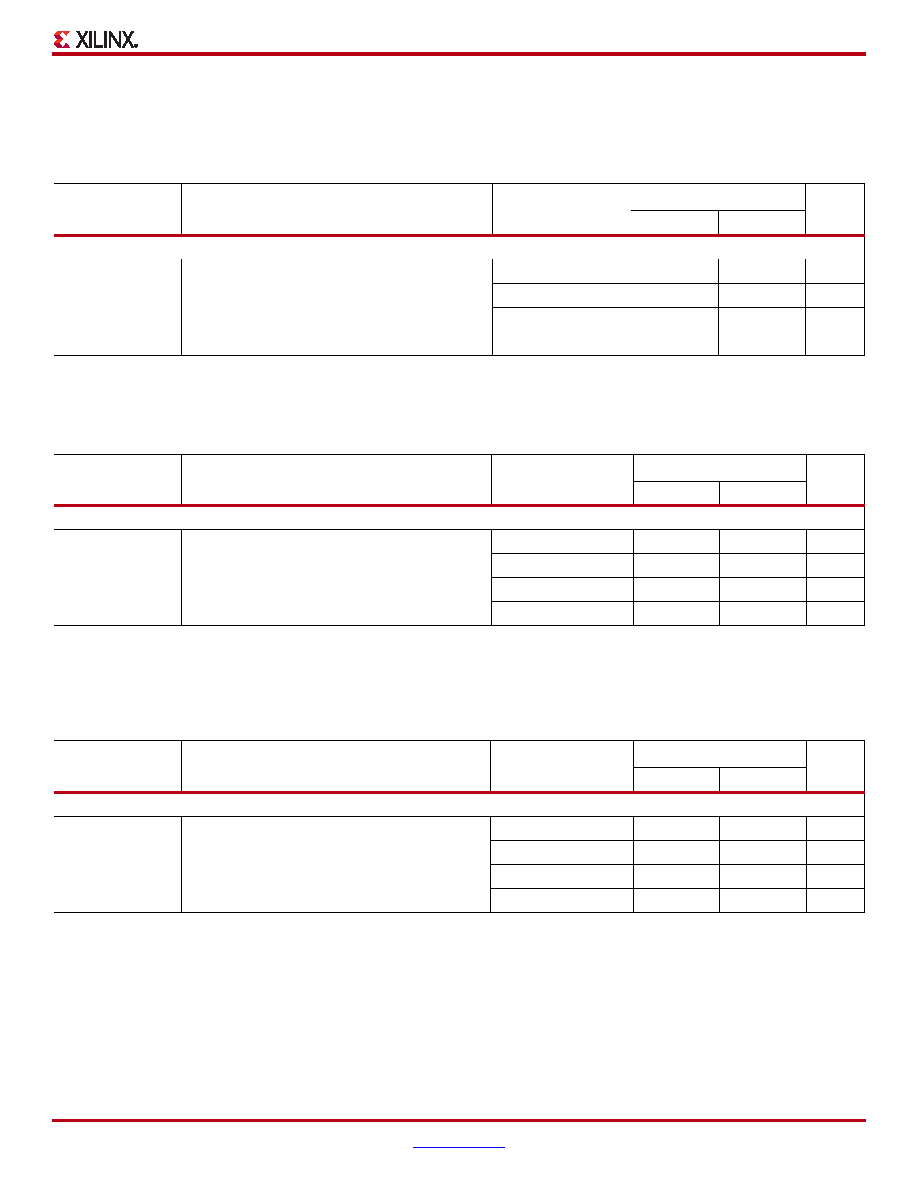

Virtex-6 CXT Device Pin-to-Pin Output Parameter Guidelines

All devices are 100% functionally tested. The representative values for typical pin locations and normal clock loading are

listed in Table 58. Values are expressed in nanoseconds unless otherwise noted.

Table 58: Global Clock Input to Output Delay Without MMCM

Symbol

Description

Device

Speed Grade

Units

-2

-1

LVCMOS25 Global Clock Input to Output Delay using Output Flip-Flop, 12mA, Fast Slew Rate, without MMCM.

TICKOF

Global Clock input and OUTFF without MMCM

XC6VCX75T

5.88

ns

XC6VCX130T

6.00

ns

XC6VCX195T

6.13

ns

XC6VCX240T

6.13

ns

Notes:

1.

Listed above are representative values where one global clock input drives one vertical clock line in each accessible column, and where all

accessible IOB and CLB flip-flops are clocked by the global clock net.

Table 59: Global Clock Input to Output Delay With MMCM

Symbol

Description

Device

Speed Grade

Units

-2

-1

LVCMOS25 Global Clock Input to Output Delay using Output Flip-Flop, 12mA, Fast Slew Rate, with MMCM.

TICKOFMMCMGC

Global Clock Input and OUTFF with MMCM

XC6VCX75T

2.77

ns

XC6VCX130T

2.78

ns

XC6VCX195T

2.78

ns

XC6VCX240T

2.79

ns

Notes:

1.

Listed above are representative values where one global clock input drives one vertical clock line in each accessible column, and where all

accessible IOB and CLB flip-flops are clocked by the global clock net.

2.

MMCM output jitter is already included in the timing calculation.

Table 60: Clock-Capable Clock Input to Output Delay With MMCM

Symbol

Description

Device

Speed Grade

Units

-2

-1

LVCMOS25 Clock-capable Clock Input to Output Delay using Output Flip-Flop, 12mA, Fast Slew Rate, with MMCM.

TICKOFMMCMCC

Clock-capable Clock Input and OUTFF with

MMCM

XC6VCX75T

2.63

ns

XC6VCX130T

2.65

ns

XC6VCX195T

2.65

ns

XC6VCX240T

2.65

ns

Notes:

1.

Listed above are representative values where one global clock input drives one vertical clock line in each accessible column, and where all

accessible IOB and CLB flip-flops are clocked by the global clock net.

2.

MMCM output jitter is already included in the timing calculation.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC4VLX60-11FF668I | IC FPGA VIRTEX-4LX 668FFBGA |

| XC4VLX60-12FFG668C | IC FPGA VIRTEX-4 LX 60K 668FCBGA |

| XC4VLX60-11FFG668I | IC FPGA VIRTEX-4 LX 60K 668FCBGA |

| XC6VCX240T-1FFG784C | IC FPGA VIRTEX 6 241K 784FFGBGA |

| XC5VSX50T-2FFG665C | IC FPGA VIRTEX-5 50K 665FCBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC6VCX195T | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-6 CXT Family Data Sheet |

| XC6VCX195T-1FF1156C | 制造商:Xilinx 功能描述:FPGA VIRTEX?-6 CXT FAMILY 199680 CELLS 40NM (CMOS) TECHNOLOG - Trays 制造商:Xilinx 功能描述:IC FPGA VIRTEX 6 195K 1156BGA |

| XC6VCX195T-1FF1156I | 制造商:Xilinx 功能描述:FPGA VIRTEX?-6 CXT FAMILY 199680 CELLS 40NM (CMOS) TECHNOLOG - Trays 制造商:Xilinx 功能描述:IC FPGA VIRTEX 6 195K 1156BGA |

| XC6VCX195T-1FF784C | 制造商:Xilinx 功能描述:FPGA VIRTEX?-6 CXT FAMILY 199680 CELLS 40NM (CMOS) TECHNOLOG - Trays 制造商:Xilinx 功能描述:IC FPGA VIRTEX 6 195K 784BGA |

| XC6VCX195T-1FF784I | 制造商:Xilinx 功能描述:FPGA VIRTEX?-6 CXT FAMILY 199680 CELLS 40NM (CMOS) TECHNOLOG - Trays 制造商:Xilinx 功能描述:IC FPGA VIRTEX 6 195K 784BGA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。