- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4292 > XC3S250E-4TQ144I (Xilinx Inc)IC FPGA SPARTAN 3E 144TQFP PDF資料下載

參數(shù)資料

| 型號(hào): | XC3S250E-4TQ144I |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 220/227頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA SPARTAN 3E 144TQFP |

| 標(biāo)準(zhǔn)包裝: | 60 |

| 系列: | Spartan®-3E |

| LAB/CLB數(shù): | 612 |

| 邏輯元件/單元數(shù): | 5508 |

| RAM 位總計(jì): | 221184 |

| 輸入/輸出數(shù): | 108 |

| 門數(shù): | 250000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 144-LQFP |

| 供應(yīng)商設(shè)備封裝: | 144-TQFP(20x20) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)第206頁(yè)第207頁(yè)第208頁(yè)第209頁(yè)第210頁(yè)第211頁(yè)第212頁(yè)第213頁(yè)第214頁(yè)第215頁(yè)第216頁(yè)第217頁(yè)第218頁(yè)第219頁(yè)當(dāng)前第220頁(yè)第221頁(yè)第222頁(yè)第223頁(yè)第224頁(yè)第225頁(yè)第226頁(yè)第227頁(yè)

Spartan-3E FPGA Family: Functional Description

DS312 (v4.1) July 19, 2013

Product Specification

92

Stepping 0 Limitations when Reprogramming via

JTAG if FPGA Set for BPI Configuration

The FPGA can always be reprogrammed via the JTAG port,

regardless of the mode pin (M[2:0]) settings. However,

Stepping 0 devices have a minor limitation. If a Stepping 0

FPGA is set to configure in BPI mode and the FPGA is

attached to a parallel memory containing a valid FPGA

configuration file, then subsequent reconfigurations using

the JTAG port will fail. Potential workarounds include setting

the mode pins for JTAG configuration (M[2:0] = <1:0:1>) or

offsetting the initial memory location in Flash by 0x2000.

Stepping 1 devices fully support JTAG configuration even

when the FPGA mode pins are set for BPI mode.

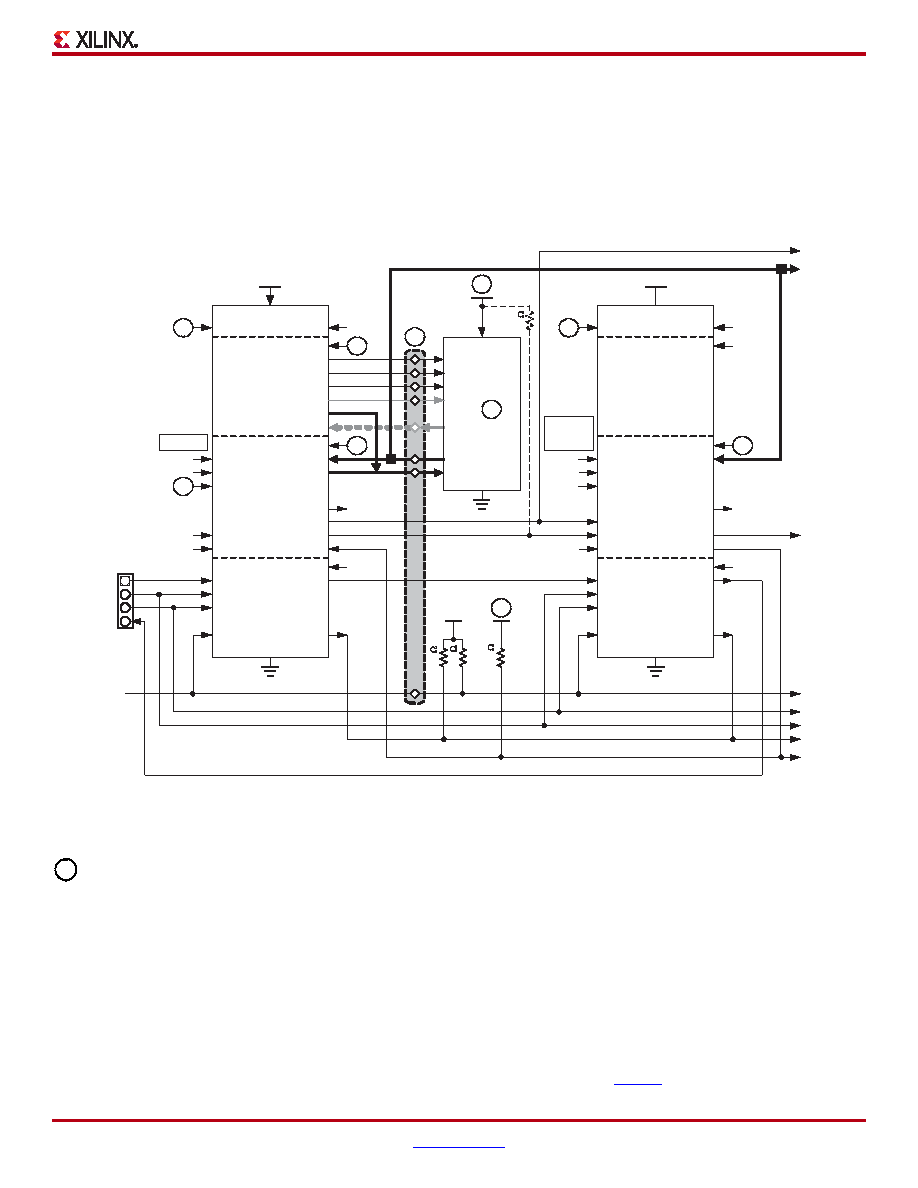

In-System Programming Support

In a production application, the parallel Flash PROM is

usually preprogrammed before it is mounted on the printed

circuit board. In-system programming support is available

from third-party boundary-scan tool vendors and from some

third-party PROM programmers using a socket adapter with

attached wires. To gain access to the parallel Flash signals,

drive the FPGA’s PROG_B input Low with an open-drain

driver. This action places all FPGA I/O pins, including those

attached to the parallel Flash, in high-impedance (Hi-Z). If

the HSWAP input is Low, the I/Os have pull-up resistors to

the VCCO input on their respective I/O bank. The external

programming hardware then has direct access to the

parallel Flash pins. The programming access points are

highlighted in the gray boxes in Figure 58 and Figure 59.

The FPGA itself can also be used as a parallel Flash PROM

programmer during development and test phases. Initially,

an FPGA-based programmer is downloaded into the FPGA

via JTAG. Then the FPGA performs the Flash PROM

programming algorithms and receives programming data

from the host via the FPGA’s JTAG interface. See the

Embedded System Tools Reference Manual.

Dynamically Loading Multiple Configuration

Images Using MultiBoot Option

For additional information, refer to the “Reconfiguration and

MultiBoot” chapter in UG332.

X-Ref Target - Figure 59

Figure 59: Daisy-Chaining from BPI Flash Mode

+2.5V

TDI

TDO

TMS

TCK

VCCINT

VCCAUX

+2.5V

HDC

CCLK

CSO_B

VCCO_1

INIT_B

CSI_B

D[7:0]

LDC1

LDC0

‘0’

A[16:0]

PROG_B

DONE

GND

VCCO_2

+1.2V

DQ[7:0]

A[n:0]

CE#

WE#

VCC

OE#

BYTE#

DQ[15:7]

GND

M2

M1

‘0’

‘1’

M0

HSWAP

VCCO_0

A

A[23:17]

P

LDC2

TDI

TDO

TMS

TCK

VCCINT

VCCAUX

CCLK

CSO_B

VCCO_1

INIT_B

CSI_B

D[7:0]

PROG_B

DONE

GND

VCCO_2

+1.2V

M2

M1

‘1’

M0

HSWAP

VCCO_0

P

VCCO_1

+2.5V

‘0’

VCCO_0

V

D

V

BPI Mode

Slave

Parallel

Mode

2.5V

JTAG

CCLK

D[7:0]

INIT_B

DONE

PROG_B

TCK

TMS

x8 or

x8/x16

Flash

PROM

PROG_B

Recommend

open-drain

driver

VCCO_0

TDI

TMS

TCK

TDO

RDWR_B

‘0’

CSO_B

RDWR_B

‘0’

BUSY

Spartan-3E

FPGA

Spartan-3E

FPGA

BUSY

I

33

0

4.

7

k

4.

7

k

Not available

in VQ100

package

DS312-2_50_082009

4.

7

k

I

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC3S250E-5TQG144C | IC FPGA SPARTAN-3E 250K 144-TQFP |

| 34VL02T/ST | IC EEPROM 2KBIT 400KHZ 8TSSOP |

| XC3S250E-5CPG132C | IC FPGA SPARTAN-3E 250K 132CSBGA |

| 34VL02T/MS | IC EEPROM 2KBIT 400KHZ 8MSOP |

| XC3S250E-4TQG144I | IC FPGA SPARTAN-3E 250K 144-TQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC3S250E-4TQG144C | 功能描述:IC SPARTAN-3E FPGA 250K 144TQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:Spartan®-3E 標(biāo)準(zhǔn)包裝:60 系列:XP LAB/CLB數(shù):- 邏輯元件/單元數(shù):10000 RAM 位總計(jì):221184 輸入/輸出數(shù):244 門數(shù):- 電源電壓:1.71 V ~ 3.465 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:388-BBGA 供應(yīng)商設(shè)備封裝:388-FPBGA(23x23) 其它名稱:220-1241 |

| XC3S250E-4TQG144I | 功能描述:IC FPGA SPARTAN-3E 250K 144-TQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:Spartan®-3E 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC3S250E-4VQ100C | 制造商:Xilinx 功能描述:FPGA SPARTAN-3E 250K GATES 5508 CELLS 572MHZ 90NM 1.2V 100VT - Trays |

| XC3S250E-4VQ100I | 功能描述:IC FPGA SPARTAN 3E 100VQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:Spartan®-3E 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC3S250E-4VQG100C | 功能描述:IC SPARTAN-3E FPGA 250K 100VQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:Spartan®-3E 標(biāo)準(zhǔn)包裝:60 系列:XP LAB/CLB數(shù):- 邏輯元件/單元數(shù):10000 RAM 位總計(jì):221184 輸入/輸出數(shù):244 門數(shù):- 電源電壓:1.71 V ~ 3.465 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:388-BBGA 供應(yīng)商設(shè)備封裝:388-FPBGA(23x23) 其它名稱:220-1241 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。