- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄140355 > WED3DL644V10BC (WHITE ELECTRONIC DESIGNS CORP) 4M X 64 SYNCHRONOUS DRAM, 7 ns, PBGA153 PDF資料下載

參數(shù)資料

| 型號: | WED3DL644V10BC |

| 廠商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分類: | DRAM |

| 英文描述: | 4M X 64 SYNCHRONOUS DRAM, 7 ns, PBGA153 |

| 封裝: | 17 X 23 MM, BGA-153 |

| 文件頁數(shù): | 14/28頁 |

| 文件大小: | 918K |

| 代理商: | WED3DL644V10BC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

21

White Electronic Designs Corporation (602) 437-1520 www.wedc.com

White Electronic Designs

WED3DL644V

August 2005

Rev. 6

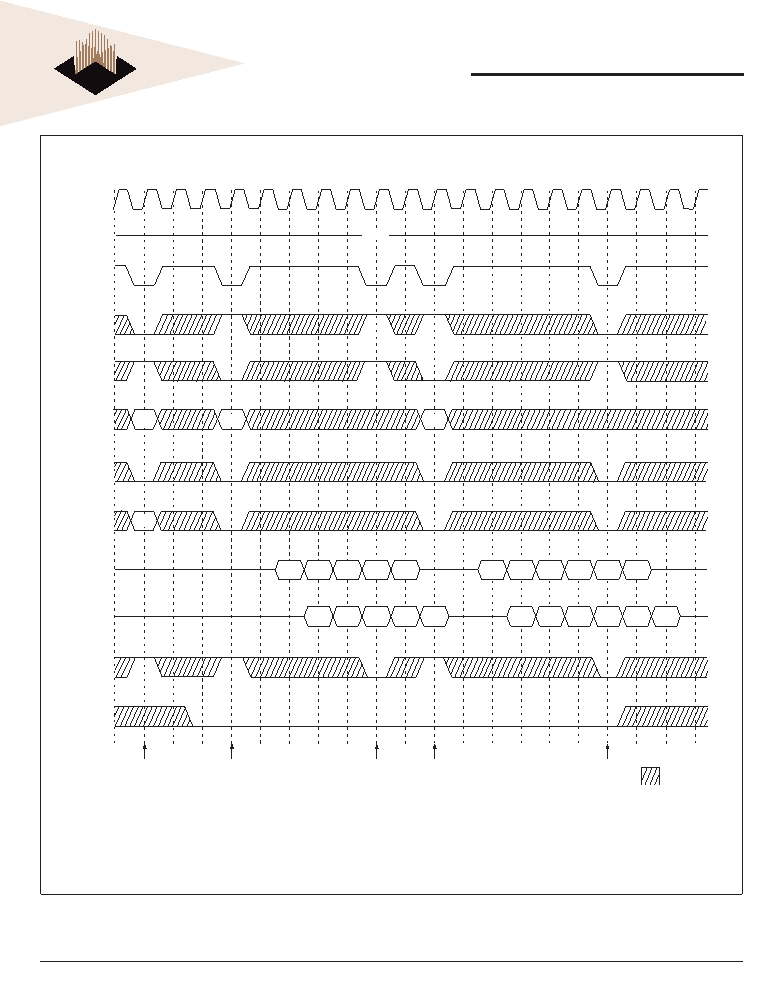

FIG. 12 READ INTERRUPTED BY PRECHARGE COMMAND & READ BURST STOP

@BURST LENGTH=FULL PAGE

RAS#

CAS#

ADDR

BA

DQM

A10/AP

CKE

CLOCK

CE#

CAb

CAa

RAa

CL = 2

Precharge

(A-Bank)

Read

(A-Bank)

Burst Stop

Read

(A-Bank)

Row Active

(A-Bank)

WE#

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

HIGH

DON'T CARE

RAa

QAa0

QAa1

QAa2

QAa3

QAa4

QAb1

QAb0

QAb3

QAb2

QAb5

QAb4

CL = 3

DQ

QAa0

QAa1

QAa2

QAa3

QAa4

QAb1

QAb0

QAb3

QAb2

QAb5

QAb4

Note 3

1

2

NOTES:

1.

At full page mode, burst is end at the end of burst. So auto precharge is possible.

2.

About the valid DQs after burst stop, it is same as the case of RAS# interrupt.

Both cases are illustrated in above timing diagram. See the label 1, 2.

But at burst write, Burst stop and RAS# interrupt should be compared carefully.

Refer to the timing diagram of "Full page write burst stop cycle."

3.

Burst stop is valid at every burst length.

相關PDF資料 |

PDF描述 |

|---|---|

| W29GL032CT7A | 2M X 16 FLASH 3V PROM, 80 ns, PBGA48 |

| WME128K8-150CCA | 128K X 8 EEPROM 5V, 150 ns, CDIP32 |

| WMS512K8VL-100DECEA | 512K X 8 STANDARD SRAM, 100 ns, CDSO32 |

| WMS512K8VL-85DECE | 512K X 8 STANDARD SRAM, 85 ns, CDSO32 |

| WF2M32B-90HM5A | 8M X 8 FLASH 5V PROM MODULE, 90 ns, CPGA66 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| WED3DL644V10BI | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:4Mx64 SDRAM |

| WED3DL644V7BC | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:4Mx64 SDRAM |

| WED3DL644V7BI | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:4Mx64 SDRAM |

| WED3DL644V8BC | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:4Mx64 SDRAM |

| WED3DL644V8BI | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:4Mx64 SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。