- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄68427 > W25Q128BVFAP (WINBOND ELECTRONICS CORP) 128M X 1 SPI BUS SERIAL EEPROM, PDSO16 PDF資料下載

參數(shù)資料

| 型號(hào): | W25Q128BVFAP |

| 廠商: | WINBOND ELECTRONICS CORP |

| 元件分類(lèi): | PROM |

| 英文描述: | 128M X 1 SPI BUS SERIAL EEPROM, PDSO16 |

| 封裝: | 0.300 INCH, GREEN, SOIC-16 |

| 文件頁(yè)數(shù): | 58/74頁(yè) |

| 文件大?。?/td> | 855K |

| 代理商: | W25Q128BVFAP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)當(dāng)前第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)

W25Q128BV

Publication Release Date: April 01, 2011

- 61 -

Revision E

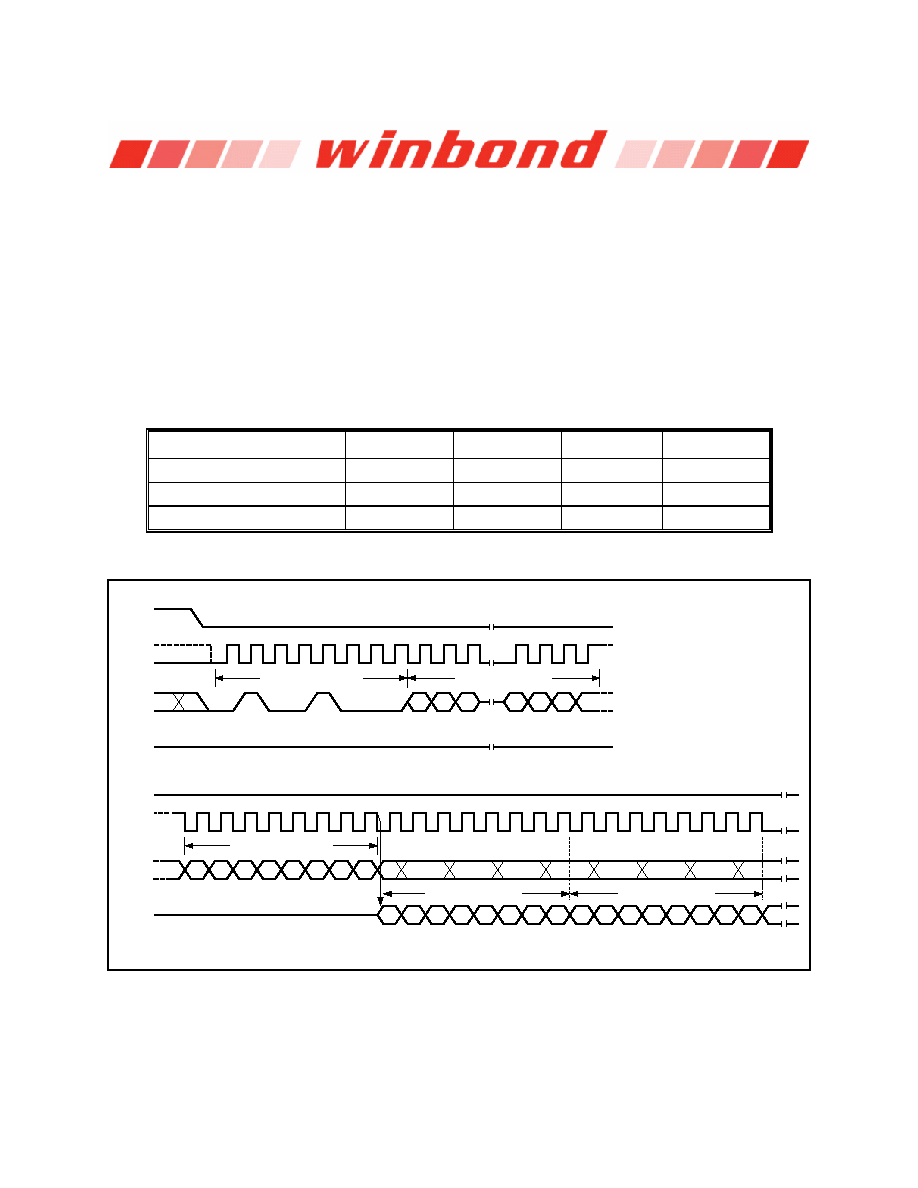

7.2.39 Read Security Registers (48h)

The Read Security Register instruction is similar to the Fast Read instruction and allows one or more data

bytes to be sequentially read from one of the three security registers. The instruction is initiated by driving

the /CS pin low and then shifting the instruction code “48h” followed by a 24-bit address (A23-A0) and

eight “dummy” clocks into the DI pin. The code and address bits are latched on the rising edge of the CLK

pin. After the address is received, the data byte of the addressed memory location will be shifted out on

the DO pin at the falling edge of CLK with most significant bit (MSB) first. The byte address is

automatically incremented to the next byte address after each byte of data is shifted out. Once the byte

address reaches the last byte of the register (byte FFh), it will reset to 00h, the first byte of the register,

and continue to increment. The instruction is completed by driving /CS high. The Read Security Register

instruction sequence is shown in Figure 37. If a Read Security Register instruction is issued while an

Erase, Program or Write cycle is in process (BUSY=1) the instruction is ignored and will not have any

effects on the current cycle. The Read Security Register instruction allows clock rates from D.C. to a

maximum of FR (see AC Electrical Characteristics).

ADDRESS

A23-16

A15-12

A11-8

A7-0

Security Register #1

00h

0 0 0 1

0 0 0 0

Byte Address

Security Register #2

00h

0 0 1 0

0 0 0 0

Byte Address

Security Register #3

00h

0 0 1 1

0 0 0 0

Byte Address

/CS

CLK

DI

(IO

0)

DO

(IO

1)

Mode 0

Mode 3

0

1

2

3

4

5

6

7

Instruction (48h)

High Impedance

8

9

10

28

29

30

31

24-Bit Address

23

22

21

3

2

1

0

Data Out 1

*

/CS

CLK

DI

(IO

0)

DO

32

(IO

1)

33

34

35

36

37

38

39

Dummy Byte

High Impedance

40

41

42

44

45

46

47

48

49

50

51

52

53

54

55

7

6

5

4

3

2

1

0

7

Data Out 2

*

7

6

5

4

3

2

1

0

*

7

6

5

4

3

2

1

0

43

31

0

= MSB

*

Figure 37. Read Security Registers Instruction Sequence

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W25Q128BVEIP | 128M X 1 SPI BUS SERIAL EEPROM, PDSO8 |

| W25Q128BVFIP | 128M X 1 SPI BUS SERIAL EEPROM, PDSO16 |

| W25Q16CLSFIP | 16M X 1 SPI BUS SERIAL EEPROM, PDSO16 |

| W25Q16CLDAIG | 16M X 1 SPI BUS SERIAL EEPROM, PDIP8 |

| W25Q16CLZPIP | 16M X 1 SPI BUS SERIAL EEPROM, PDSO8 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W25Q128BVFIG | 制造商:Winbond Electronics Corp 功能描述:Flash Serial-SPI 3.3V 128Mbit 16M x 8bit 8.5ns 16-Pin SOIC 制造商:Winbond Electronics Corp 功能描述:128MB SPI FLASH |

| W25Q128BVFIP | 制造商:WINBOND 制造商全稱(chēng):Winbond 功能描述:3V 128M-BIT SERIAL FLASH MEMORY WITH DUAL AND QUAD SPI |

| W25Q128FV | 制造商:WINBOND 制造商全稱(chēng):Winbond 功能描述:SERIAL FLASH MEMORY WITH DUAL/QUAD SPI & QPI |

| W25Q128FVAIG | 制造商:WINBOND 制造商全稱(chēng):Winbond 功能描述:3V 128M-BIT SERIAL FLASH MEMORY WITH DUAL/QUAD SPI & QPI |

| W25Q128FVAIP | 制造商:WINBOND 制造商全稱(chēng):Winbond 功能描述:3V 128M-BIT SERIAL FLASH MEMORY WITH DUAL/QUAD SPI & QPI |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。