- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359354 > VDP3104B (MICRONAS SEMICONDUCTOR HOLDING AG) Video Processor Family PDF資料下載

參數(shù)資料

| 型號: | VDP3104B |

| 廠商: | MICRONAS SEMICONDUCTOR HOLDING AG |

| 元件分類: | 消費家電 |

| 英文描述: | Video Processor Family |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PDIP64 |

| 封裝: | SHRINK, PLASTIC, DIP-64 |

| 文件頁數(shù): | 18/72頁 |

| 文件大?。?/td> | 603K |

| 代理商: | VDP3104B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁

PRELIMINARY DATA SHEET

VDP 31xxB

18

Micronas

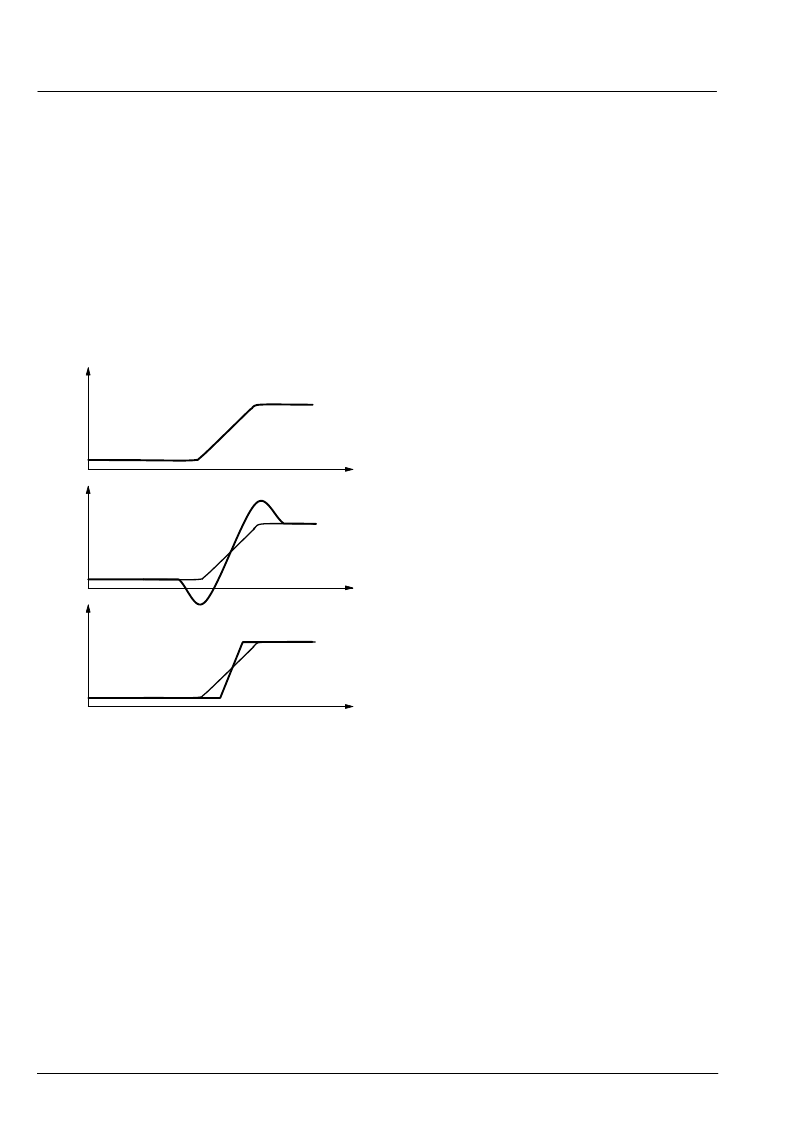

2.8.8. Chroma Transient Improvement

The intention of this block is to enhance the chroma

resolution. A correction signal is calculated by differenti-

ation of the color difference signals. The differentiation

can be selected according to the signal bandwidth, e.g.

for PAL/NTSC/SECAM or digital component signals,

respectively. The amplitude of the correction signal is

adjustable. Small noise amplitudes in the correction sig-

nal are suppressed by an adjustable coring circuit. To

eliminate

‘

wrong colors

’

, which are caused by over and

undershoots at the chroma transition, the sharpened

chroma signals are limited to a proper value automati-

cally.

Fig. 2

–

18:

Digital Color Transient Improvement

t

t

t

Cr out

Cb out

Ampl.

Cr in

Cb in

a)

b)

c)

a) Cr Cb input of DTI

b) Cr Cb input

c) sharpened and limited Cr Cb

Correction signal

2.8.9. Inverse Matrix

A 6-multiplier matrix transcodes the Cr and Cb signals

to R

–

Y, B

–

Y, and G

–

Y. The multipliers are also used to

adjust color saturation in the range of 0 to 2. The coeffi-

cients are signed and have a resolution of 9 bits. There

are separate matrix coefficients for main and side pic-

tures. The matrix computes:

R

–

Y

G

–

Y

B

–

Y

MR1*Cb

MG1*Cb

MB1*Cb

MR2*Cr

MG2*Cr

MB2*Cr

The initialization values for the matrix are computed

from the standard ITUR (CCIR) matrix:

R

G

B

1

1

1

0

0.345

1.773

1.402

0.713

0

Y

Cb

Cr

For a contrast setting of CTM

scaled by a factor of 64, see also table 3

–

1.

32, the matrix values are

2.8.10. RGB Processing

After adding the post-processed luma, the digital RGB

signals are limited to 10 bits. Three multipliers are used

to digitally adjust the white drive. Using the same multi-

pliers an average beam current limiter is implemented.

See also section 2.9.1.

‘

CRT Measurement and Con-

trol

’

.

2.8.11. OSD Color Lookup Table

The VDP 31xxB has five input lines for an OSD signal.

This signal forms a 5-bit address for a color look-up table

(CLUT). The CLUT is a memory with 32 words where

each word holds a RGB value.

Bits 0 to 3 (bit 4

of the OSD, which generates full RGB signals (bit 0 to 2)

and half-contrast RGB signals (bit 3).

0) form the addresses for the ROM part

Bit 4 addresses the RAM part of the OSD with 16 freely

programmable colors, addressable with bit 0 to 3. The

programming is done via the I

2

C-bus.

The amplitude of the CLUT output signals can be ad-

justed separately for R, G and B via the I

2

C-bus. The

switchover between video RGB and OSD RGB is done

via the Priority bus.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VDP3108 | Single-Chip Video Processor |

| VDP3130Y | Video Processor Family |

| VDP31XXB | Video Processor Family |

| VDP3108PR | Consumer IC |

| VDSGLD_38.88 | TRANS PREBIASED PNP 200MW SOT23 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VDP3108 | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Single-Chip Video Processor |

| VDP3108B | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video Processor Family |

| VDP3108PR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Consumer IC |

| VDP3112B | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video Processor Family |

| VDP3116B | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video Processor Family |

發(fā)布緊急采購,3分鐘左右您將得到回復。