- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359354 > VDP3104B (MICRONAS SEMICONDUCTOR HOLDING AG) Video Processor Family PDF資料下載

參數(shù)資料

| 型號(hào): | VDP3104B |

| 廠商: | MICRONAS SEMICONDUCTOR HOLDING AG |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | Video Processor Family |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PDIP64 |

| 封裝: | SHRINK, PLASTIC, DIP-64 |

| 文件頁(yè)數(shù): | 14/72頁(yè) |

| 文件大?。?/td> | 603K |

| 代理商: | VDP3104B |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)

VDP 31xxB

PRELIMINARY DATA SHEET

14

Micronas

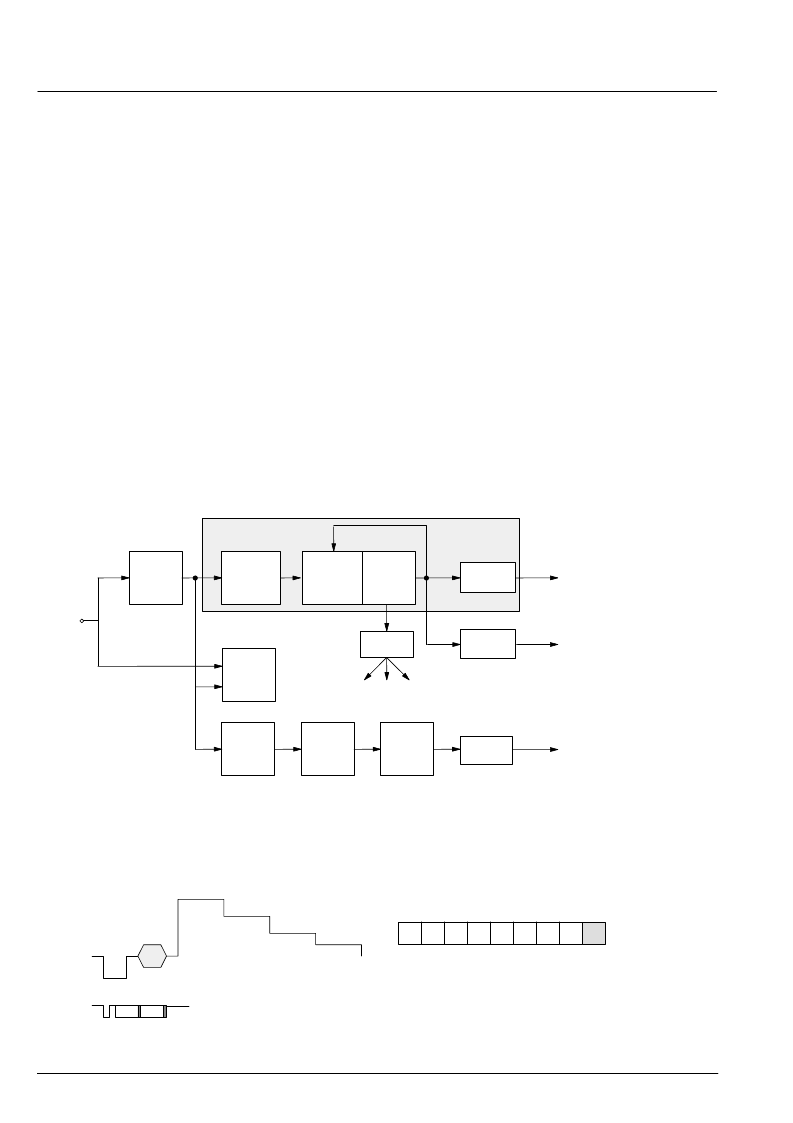

2.7. Video Sync Processing

Fig. 2

–

11 shows a block diagram of the front-end sync

processing. To extract the sync information from the

video signal, a linear phase lowpass filter eliminates all

noise and video contents above 1 MHz. The sync is sep-

arated by a slicer; the sync phase is measured. A vari-

able window can be selected to improve the noise immu-

nity of the slicer. The phase comparator measures the

falling edge of sync, as well as the integrated sync pulse.

The sync phase error is filtered by a phase-locked loop

that is computed by the FP. All timing in the front-end is

derived from a counter that is part of this PLL, and it thus

counts synchronously to the video signal.

A separate hardware block measures the signal back

porch and also allows gathering the maximum/minimum

of the video signal. This information is processed by the

FP and used for gain control and clamping.

For vertical sync separation, the sliced video signal is in-

tegrated. The FP uses the integrator value to derive ver-

tical sync and field information.

The information extracted by the video sync processing

is multiplexed onto the hardware front sync signal (FSY)

and is distributed to the rest of the video processing sys-

tem. The format of the front sync signal is given in

Fig. 2

–

12.

The data for the vertical deflection, the sawtooth, and the

East-West correction signal is calculated by the

VDP 31xxB. The data is buffered in a FIFO and trans-

ferred to the back-end by a single wire interface.

Frequency and phase characteristics of the analog vid-

eo signal are derived from PLL1. The results are fed to

the scaler unit for data interpolation and orthogonaliza-

tion and to the clock synthesizer for line-locked clock

generation. Horizontal and vertical syncs are latched

with the line-locked clock.

phase

comparator

&

lowpass

counter

front-end

timing

front sync

skew

vblank

field

lowpass

1 MHz

&

syncslicer

horizontal

sync

separation

vertical

sync

separation

FIFO

Sawtooth

Parabola

Calculation

video

input

front

sync

generator

vertical

serial

data

vertical

E/W

sawtooth

clamping, colorkey, FIFO_write

PLL1

clamp &

signal

meas.

Fig. 2

–

11:

Sync separation block diagram

clock

synthesizer

syncs

clock

H/V syncs

F1

(not in scale)

input

analog

video

FSY

F1

Parity

V: vertical sync

0 = off

1 = on

F: field #

0 = field 1

1 = field 2

Fig. 2

–

12:

Front sync format

F0

skew

LSB

skew

MSB

not

F

V

F0 reserved

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VDP3108 | Single-Chip Video Processor |

| VDP3130Y | Video Processor Family |

| VDP31XXB | Video Processor Family |

| VDP3108PR | Consumer IC |

| VDSGLD_38.88 | TRANS PREBIASED PNP 200MW SOT23 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VDP3108 | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Single-Chip Video Processor |

| VDP3108B | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video Processor Family |

| VDP3108PR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Consumer IC |

| VDP3112B | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video Processor Family |

| VDP3116B | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video Processor Family |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。