- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄300083 > V55C1256164MGLI-75H (PROMOS TECHNOLOGIES INC) SYNCHRONOUS DRAM, PDSO54 PDF資料下載

參數(shù)資料

| 型號(hào): | V55C1256164MGLI-75H |

| 廠商: | PROMOS TECHNOLOGIES INC |

| 元件分類: | DRAM |

| 英文描述: | SYNCHRONOUS DRAM, PDSO54 |

| 封裝: | 0.400 INCH, GREEN, PLASTIC, TSSOP2-54 |

| 文件頁數(shù): | 1/48頁 |

| 文件大?。?/td> | 634K |

| 代理商: | V55C1256164MGLI-75H |

當(dāng)前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

1

V55C1256164MG

256Mbit MOBILE SDRAM

1.8 VOLT, TSOP II / FBGA PACKAGE

16M X 16

V55C1256164MG Rev. 1.0 September 2008

75910

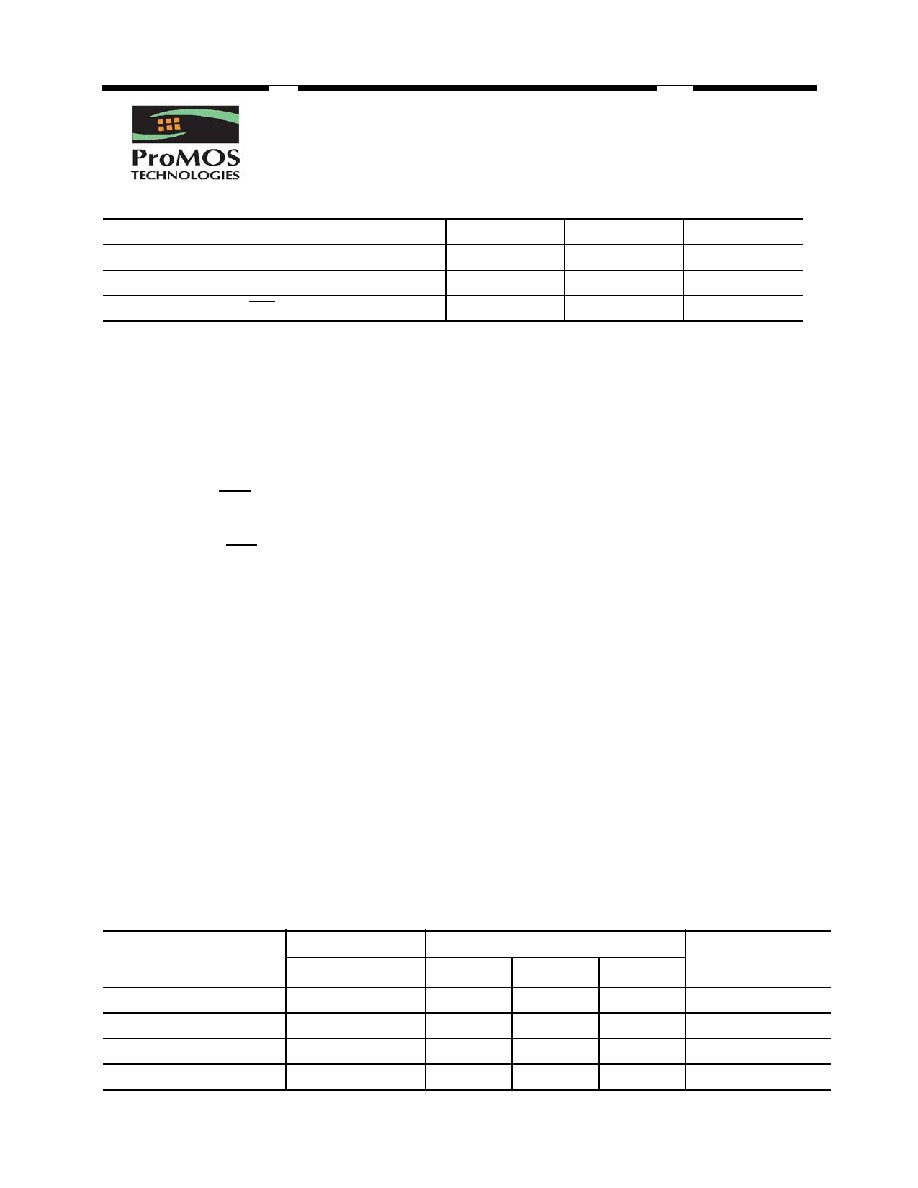

System Frequency (fCK)

133 MHz

111 MHz

100MHz

Clock Cycle Time (tCK3)

7.5ns

9.0 ns

10 ns

Clock Access Time (tAC3) CAS Latency = 3

6.0 ns

7.0 ns

8.0ns

Features

■ 4 banks x 4Mbit x 16 organization

■ High speed data transfer rates up to 133 MHz

■ Full Synchronous Dynamic RAM, with all signals

referenced to clock rising edge

■ Single Pulsed RAS Interface

■ Data Mask for Read/Write Control

■ Four Banks controlled by BA0 & BA1

■ Programmable CAS Latency:1, 2, 3

■ Programmable Wrap Sequence: Sequential or

Interleave

■ Programmable Burst Length:

1, 2, 4, 8, Full page for Sequential Type

1, 2, 4, 8 for Interleave Type

■ Multiple Burst Read with Single Write Operation

■ Automatic and Controlled Precharge Command

■ Random Column Address every CLK (1-N Rule)

■ Power Down Mode and Clock Suspend Mode

■ Auto Refresh and Self Refresh

■ Refresh Interval:

8192 cycles/64 ms [ 0 to 70

°C (Commercial)] ;

8192 cycles/64ms[-40 to 85

°C (Industrial)];

8192 cycles/32ms [-40 to 105

°C (H)];

8192 cycles/32ms [-40 to 125

°C (Extended)]

■

■ Available in 54-ball FBGA (with 9x6 ball array

with 3 depopulated rows, 8x10 mm), and 54 pin

TSOP II

■ VDD=1.8V, VDDQ=1.8V

■ LVCMOS Interface

■ Drive Strength (DS) Option: Full, 1/2, 1/4 and 1/8

■ Auto Temperature Compensated Self Refresh

(Auto TCSR)

■ Partial Array Self Refresh (PASR) option: Full,

1/2, 1/4, 1/8 and 1/16

■ Deep Power Down (DPD) mode

■ Programmable Power Reduction Feature by par-

tial array activation during Self-Refresh

■ Operating Temperature Range

Commercial (0

°C to 70°C)

Industrial (-40

°C to +85°C)

H (-40

°C to +105°C)

Extended(-40

°C to +125°C)

Device Usage Chart

Operating

Temperature

Range

Package Outline

Access Time (ns)

Temperature

Mark

K / I

75

9

10

0

°C to 70°C

-40

°C to 85°C

I

-40

°C to 105°C

H

-40

°C to 125°C

E

note: When temperature is higher than 100

°C, TCSR and self-refresh is not guaranteed.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| V55C3256164VBLG10IPC | SYNCHRONOUS DRAM, PBGA54 |

| V55C3256164VBLG8 | SYNCHRONOUS DRAM, PBGA54 |

| V55C3256164VBUC8PC | SYNCHRONOUS DRAM, PBGA54 |

| V55C3256164VBUG10E | SYNCHRONOUS DRAM, PBGA54 |

| V585ME06 | VCO, 1000 MHz - 2000 MHz |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| V55C2128164V | 制造商:MOSEL 制造商全稱:MOSEL 功能描述:128Mbit LOW-POWER SDRAM 2.5 VOLT, TSOP II / BGA PACKAGE 8M X 16 |

| V55C2128164VB | 制造商:MOSEL 制造商全稱:MOSEL 功能描述:128Mbit LOW-POWER SDRAM 2.5 VOLT, TSOP II / BGA PACKAGE 8M X 16 |

| V55C2128164VT | 制造商:MOSEL 制造商全稱:MOSEL 功能描述:128Mbit LOW-POWER SDRAM 2.5 VOLT, TSOP II / BGA PACKAGE 8M X 16 |

| V55C2256164VB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:256Mbit MOBILE SDRAM 2.5 VOLT FBGA PACKAGE 16M X 16 |

| V55HD | 制造商:Bugera 功能描述:55 WATT GUITAR AMPLIFIER 2 CHANNEL TUBE HEAD |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。