- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376430 > UPD72850AGK-9EU (NEC Corp.) Circular Connector; No. of Contacts:56; Series:MS27467; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:25; Circular Contact Gender:Pin; Circular Shell Style:Straight Plug; Insert Arrangement:25-4 RoHS Compliant: No PDF資料下載

參數(shù)資料

| 型號: | UPD72850AGK-9EU |

| 廠商: | NEC Corp. |

| 元件分類: | 圓形連接器 |

| 英文描述: | Circular Connector; No. of Contacts:56; Series:MS27467; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:25; Circular Contact Gender:Pin; Circular Shell Style:Straight Plug; Insert Arrangement:25-4 RoHS Compliant: No |

| 中文描述: | IEEE1394連接400Mbps的物理層 |

| 文件頁數(shù): | 25/48頁 |

| 文件大小: | 290K |

| 代理商: | UPD72850AGK-9EU |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

Data Sheet S14452EJ1V0DS00

25

μ

PD72850A

Acceleration Controller

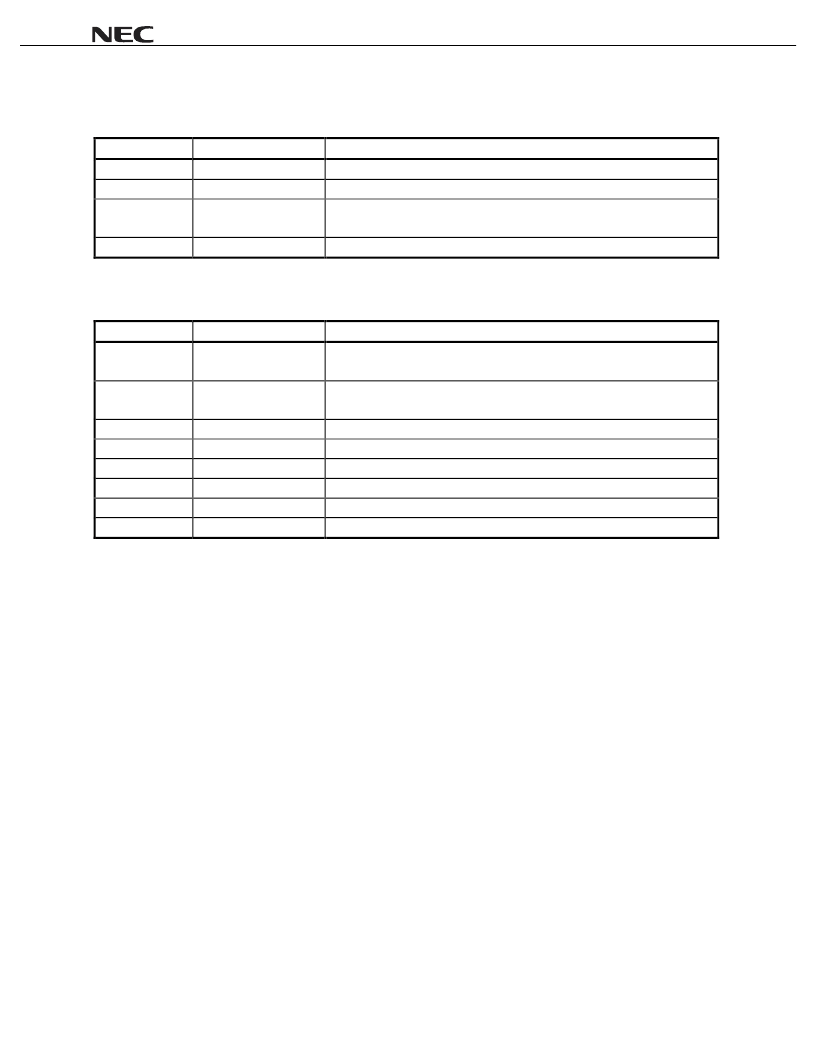

Table 4-8. Acceleration Controller Request Format

Bit

Type

Content

0

start

Signal that starts a request : 1

1-3

request

110 : Acc Ctrl accelerate controller

4

access address

0: Accelerate disable

1: Accelerate enable

5

stop

End request signal : 0

Table 4-9. Request Type List

Bit

Type

Content

000

ImmReq

Used to acknowledge packet transmit.

When Idle is detected, PHY immediately controls the bus.

001

IsoReq

Used to transmit isochronous packet.

PHY does arbitration after isochronous gap is detected and acquires the bus.

010

PriReq

Used for Cycle master request.

011

FairReq

Fair request.

100

RdReg

PHY register read request.

101

WrReg

PHY register write request.

110

AccCtrl

Disable/enable of arbitration acceleration.

111

-

Unused.

For the Link to execute Priority request and Fair, start the request using LREQ when CTL0,CTL1 becomes

idle, after one clock. When request is acknowledged, the

μ

PD72850A outputs Grant to CTL0,CTL1.

The Link of cycle master uses PriReq to transmit the cycle start packet. IsoReq transmits the isochronous

packet.

IsoReq becomes effective only as follows:

The transmission of the cycle start packet is performed on the same isochronous period as Receive. (The

period until the subaction gap is detected.)

During isochronous packet Transmit or Receive.

The

μ

PD72850A cancels IsoReq with the subaction gap detection or bus reset. To meet the timing, do not

issue the IsoReq to PHY when CRC operation is performed.

The Link cancel method is described later.

After the packet is received, Link issues ImmReq as the acknowledge packet transmission. The purpose is to

prevent another node from detecting subaction gap as ACK_RESPONSE_TIME. The

μ

PD72850A acquires

the bus after packet receive and returns Grant to CTL0,CTL1. When CRC fails, before Link detects Grant,

assert 3 Idle cycles to CTL0,CTL1.

When the bus reset is generated, the unprocessed requests are canceled.

The

μ

PD72850A updates the data of the Write request register and the contents of the Read register are

changed. The contents of the register of the specified address are output to the Link as a status transfer in the

Read request register, When the status transmission is interrupted by transmitting/receiving packets, the

status transmission will re-start from the first bit after completing the transmit/receive of the packets.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| uPD750066CU | 4-BIT SINGLE-CHIP MICROCONTROLLERS |

| uPD750068GT | 4-BIT SINGLE-CHIP MICROCONTROLLERS |

| uPD750068GTA | 4-BIT SINGLE-CHIP MICROCONTROLLERS |

| uPD750066GTA | CONNECTOR ACCESSORY |

| UPD750064 | 4-BIT SINGLE-CHIP MICROCONTROLLERS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD74HC04C | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD750068GT-396 | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD7507C189 | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD7508CU265 | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD75208 | 制造商:Panasonic Industrial Company 功能描述:IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。