- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376430 > UPD703100-33 (NEC Corp.) V850E/MS1TM 32/16-BIT SINGLE-CHIP MICROCONTROLLERS PDF資料下載

參數(shù)資料

| 型號: | UPD703100-33 |

| 廠商: | NEC Corp. |

| 英文描述: | V850E/MS1TM 32/16-BIT SINGLE-CHIP MICROCONTROLLERS |

| 中文描述: | V850E/MS1TM 32/16單晶片微控制器 |

| 文件頁數(shù): | 65/132頁 |

| 文件大小: | 1174K |

| 代理商: | UPD703100-33 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁當(dāng)前第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁

Preliminary Data Sheet U14168EJ2V0DS00

65

μ

PD703100A-33, 703100A-40, 703101A-33, 703102A-33

(6/7)

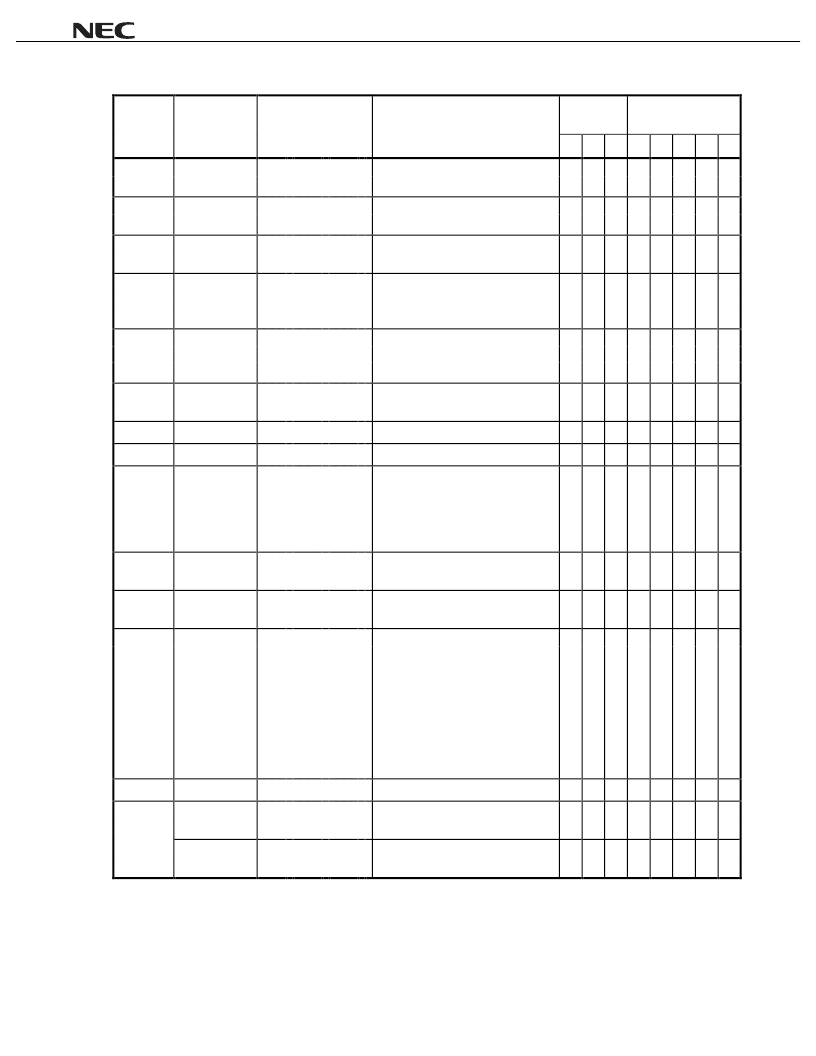

Execution

Clock

Flags

Mnemonic

Operand

Opcode

Operation

i

r

l

CY

OV

S

Z

SAT

rr r r r 1 0 0 1 d d d d d dd

SST.H

reg2,disp8[ep]

Note 19

adr

←

ep+zero-extend(disp8)

Store-memory(adr,GR[reg2],Half-word)

1

1

1

rr r r r 1 0 1 0 d d d d d d1

SST.W

reg2,disp8[ep]

Note 21

adr

←

ep+zero-extend(disp8)

Store-memory(adr,GR[reg2],Word)

1

1

1

rr r r r 1 1 1 0 1 0 R R R RR

ST.B

reg2,disp16[reg1]

dd d d d d d d d d d d d d dd

adr

←

GR[reg1]+sign-extend(disp16)

Store-memory(adr,GR[reg2],Byte)

1

1

1

rr r r r 1 1 1 0 1 1 R R R RR

dd d d d d d d d d d d d d d0

ST.H

reg2,disp16[reg1]

Note 8

adr

←

GR[reg1]+sign-extend(disp16)

Store-memory(adr,GR[reg2],Half-word)

1

1

1

rr r r r 1 1 1 0 1 1 R R R RR

dd d d d d d d d d d d d d d1

ST.W

reg2,disp16[reg1]

Note 8

adr

←

GR[reg1]+sign-extend(disp16)

Store-memory(adr,GR[reg2],Word)

1

1

1

rr r r r 1 1 1 1 1 1 R R R RR

STSR

regID,reg2

00 0 0 0 0 0 0 0 1 0 0 0 0 00

GR[reg2]

←

SR[regID]

1

1

1

SUB

reg1,reg2

rr r r r 0 0 1 1 0 1 R R R RR

GR[reg2]

←

GR[reg2]

GR[reg1]

1

1

1

×

×

×

×

SUBR

reg1,reg2

rr r r r 0 0 1 1 0 0 R R R RR

GR[reg2]

←

GR[reg1]

GR[reg2]

1

1

1

×

×

×

×

SWITCH

reg1

00 0 0 0 0 0 0 0 1 0 R R R RR

adr

←

(PC+2)+(GR[reg1] logically shift left

by 1)

PC

←

(PC+2)+(sign-extend(Load-

memory(adr,Half-word)))

logically shift left by 1

5

5

5

SXB

reg1

00 0 0 0 0 0 0 1 0 1 R R R RR

GR[reg1]

←

sign-extend

(GR[reg1] (7 : 0)

1

1

1

SXH

reg1

00 0 0 0 0 0 0 1 1 1 R R R RR

GR[reg1]

←

sign-extend

(GR[reg1] (15 : 0))

1

1

1

00 0 0 0 1 1 1 1 1 1 i i i ii

TRAP

vector

00 0 0 0 0 0 1 0 0 0 0 0 0 00

EIPC

←

PC+4 (restore PC)

←

PSW

←

Interrupt code

←

1

←

1

←

00000040H (when vector

is 00H to 0FH)

EIPSW

ECR.EICC

PSW.EP

PSW.ID

PC

00000050H (when vector

is 10H to 1FH)

3

3

3

TST

reg1,reg2

rr r r r 0 0 1 0 1 1 R R R RR

result

←

GR[reg2] AND GR[reg1]

1

1

1

0

×

×

11 b b b 1 1 1 1 1 0 R R R RR

bit#3,disp16[reg1]

dd d d d d d d d d d d d d dd

adr

←

GR[reg1]+sign-extend(disp16)

Z flag

←

Not(Load-memory-bit(adr,bit#3))

3

Note 3

3

Note 3

3

Note 3

×

rr r r r 1 1 1 1 1 1 R R R RR

TST1

reg2,[reg1]

00 0 0 0 0 0 0 1 1 1 0 0 1 10

adr

←

GR[reg1]

Z flag

←

Not(Load-memory-bit(adr,reg2))

3

Note 3

3

Note 3

3

Note 3

×

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD703100-40 | V850E/MS1TM 32/16-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD703100AF1-33-FA1 | V850E/MS1TM 32/16-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD703100AF1-40-FA1 | V850E/MS1TM 32/16-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD703100A-40 | V850E/MS1TM 32/16-BIT SINGLE-CHIP MICROCONTROLLERS |

| uPD720114GA-YEU-A | MOS INTEGRATED CIRCUIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD703100-40 | 制造商:NEC 制造商全稱:NEC 功能描述:V850E/MS1TM 32/16-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD703100A | 制造商:NEC 制造商全稱:NEC 功能描述:32-Bit Single-Chip Microcontrollers |

| UPD703100A-33 | 制造商:NEC 制造商全稱:NEC 功能描述:V850E/MS1TM 32/16-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD703100A-40 | 制造商:NEC 制造商全稱:NEC 功能描述:V850E/MS1TM 32/16-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD703100AF1-33-FA1 | 制造商:NEC 制造商全稱:NEC 功能描述:V850E/MS1TM 32/16-BIT SINGLE-CHIP MICROCONTROLLERS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。