- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361342 > T35L3232B (TM Technology, Inc.) 32K x 32 SRAM PDF資料下載

參數(shù)資料

| 型號: | T35L3232B |

| 廠商: | TM Technology, Inc. |

| 英文描述: | 32K x 32 SRAM |

| 中文描述: | 32K的× 32的SRAM |

| 文件頁數(shù): | 12/19頁 |

| 文件大小: | 261K |

| 代理商: | T35L3232B |

TE

CH

tm

Preliminary T35L3232B

Taiwan Memory Technology, Inc. reserves the right

to change products or specifications without notice.

P. 5

Publication Date: FEB. 2000

Revision:0.A

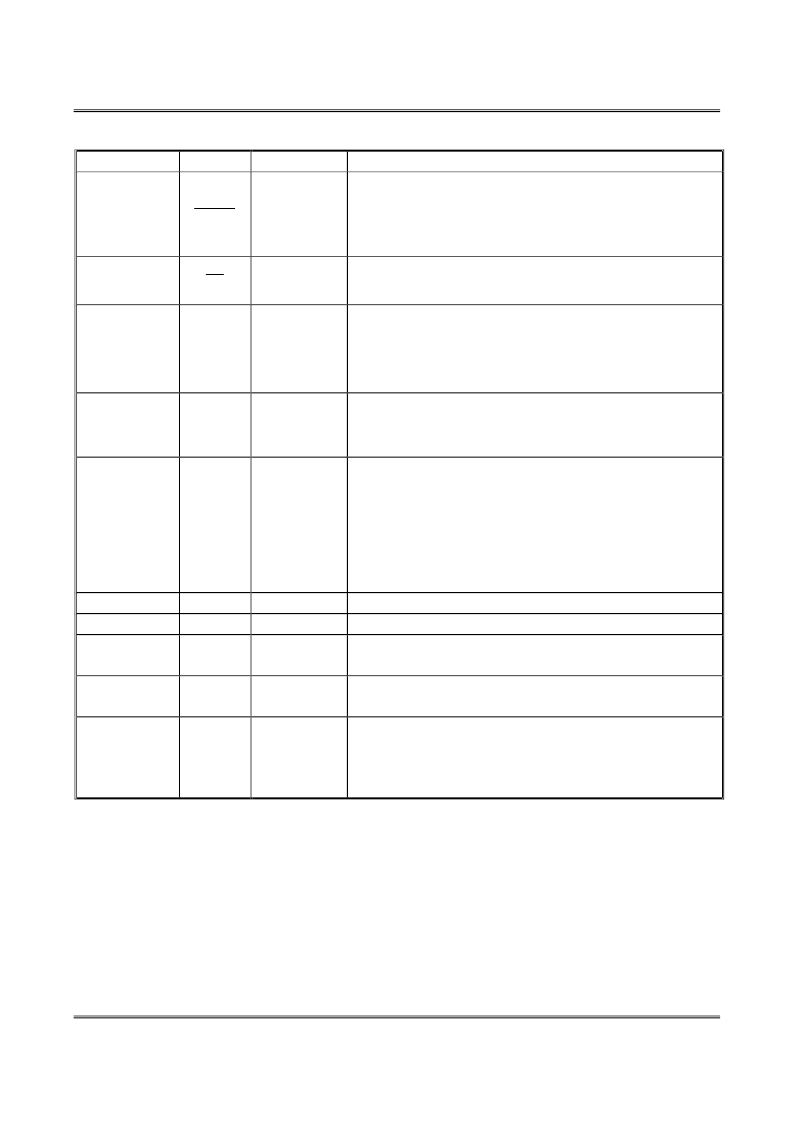

PIN DESCRIPTIONS

(continued)

QFP PINS

SYM.

TYPE

DESCRIPTION

85

ADSC

Input-

Synchronous

Address Status Controller:This active LOW input causes

device to be deselected or selected along with new external

address to be registered.

A READ or WRITE cycle is

initiated depending upon write control inputs.

14

FT

Input-

Static

A LOW on this pin selects in flow-through mode. A NC or

HIGH on this pin selects in pipeline mode.

31

MODE

Input-

Static

Mode: This input selects the burst sequence. A LOW on this

pin selects LINEAR BURST. A NC or HIGH on this pin

selects INTERLEAVED BURST. Do not alter input state

while device is operating.

64

ZZ

Input

Snooze Enable: This active HIGH asynchronous input causes

the device to enter a low-power standby mode in which all

data in the memory arry is retained.

2, 3, 6-9, 12, 13,

18, 19, 22-25,

28, 29, 52, 53,

56-59, 62, 63,

68, 69, 72-75,

78, 79,

DQ1-

DQ32

Input/

Output

Data Inputs/Outputs: First Byte is DQ1-DQ8. Second Byte is

DQ9-DQ16. Third Byte is DQ17-DQ24. Fourth Byte is DQ25-

DQ32. Input data must meet setup and hold times around the

rising edge of CLK.

15,41,65,91

17,40,67,90

4,11,20,27,54,

61,70,77

5,10,21,26,55,

60,71,76

VCC

VSS

Supply

Ground

Power Supply: 3.3V +10%/-5%

Ground: GND

VCCQ

I/O Supply

Output Buffer Supply: 3.3V +10%/-5%

VSSQ

I/O Ground

Output Buffer Ground: GND

1,16,30,38,

39,42,43,49,

50, 51, 66,80

NC

-

No Connect: These signals are not internally conntected.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T35L3232B-3.8Q | 32K x 32 SRAM |

| T35L3232B-4T | 32K x 32 SRAM |

| T35L6432A | 64K x 32 SRAM |

| T35L6432A-5Q | 64K x 32 SRAM |

| T35L6432A-5T | 64K x 32 SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T35L3232B-3.8Q | 制造商:TMT 制造商全稱:TMT 功能描述:32K x 32 SRAM |

| T35L3232B-4T | 制造商:TMT 制造商全稱:TMT 功能描述:32K x 32 SRAM |

| T35L6432A | 制造商:TMT 制造商全稱:TMT 功能描述:64K x 32 SRAM |

| T35L6432A-5Q | 制造商:TMT 制造商全稱:TMT 功能描述:64K x 32 SRAM |

| T35L6432A-5T | 制造商:TMT 制造商全稱:TMT 功能描述:64K x 32 SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。