- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25648 > STM32W108HBU7 (STMICROELECTRONICS) SPECIALTY MICROPROCESSOR CIRCUIT, QCC40 PDF資料下載

參數(shù)資料

| 型號(hào): | STM32W108HBU7 |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, QCC40 |

| 封裝: | 6 X 6 MM, 0.50 MM PITCH, ROHS COMPLIANT, VFQFPN-40 |

| 文件頁(yè)數(shù): | 4/198頁(yè) |

| 文件大小: | 2871K |

| 代理商: | STM32W108HBU7 |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)

STM32W108CB, STM32W108HB

General-purpose timers

Doc ID 16252 Rev 3

101/198

Register (TIM2_OR) has four single bit fields (TIM_REMAPCy) that control whether a Timer

2 channel is mapped to its default GPIO in port PA, or remapped to a GPIO in PB.

Table 23 specifies the pins that may be assigned to Timer 1 and Timer 2 functions.

The TIMxCLK and TIMxMSK inputs can be used only in the external clock modes: refer to

the External Clock Source Mode 1 and External Clock Source Mode 2 sections for details

concerning their use.

10.1.1

Time-base unit

The main block of the general purpose timer is a 16-bit counter with its related auto-reload

register. The counter can count up, down, or alternate up and down. The counter clock can

be divided by a prescaler.

The counter, the auto-reload register, and the prescaler register can be written to or read by

software. This is true even when the counter is running.

The time-base unit includes:

●

Counter register (TIMx_CNT)

●

Prescaler register (TIMx_PSC)

●

Auto-reload register (TIMx_ARR)

Some timer registers cannot be directly accessed by software, which instead reads and

writes a "buffer register". The internal registers actually used for timer operations are called

"shadow registers".

The auto-reload register is buffered. Writing to or reading from the auto-reload register

accesses the buffer register. The contents of the buffer register are transferred into the

shadow register permanently or at each update event (UEV), depending on the auto-reload

buffer enable bit (TIM_ARBE) in the TIMx_CR1 register. The update event is generated

when both the counter reaches the overflow (or underflow when down-counting) and when

the TIM_UDIS bit equals 0 in the TIMx_CR1 register. It can also be generated by software.

Update event generation is described in detail for each configuration.

The counter is clocked by the prescaler output CK_CNT, which is enabled only when the

counter enable bit (TIM_CEN) in the TIMx_CR1 register is set. Refer also to the slave mode

controller description in the Timers and External Trigger Synchronization section to get more

details on counter enabling.

Note that the actual counter enable signal CNT_EN is set one clock cycle after TIM_CEN.

Note:

When the STM32W108 enters debug mode and the ARM Cortex-M3 core is halted, the

counters continue to run normally.

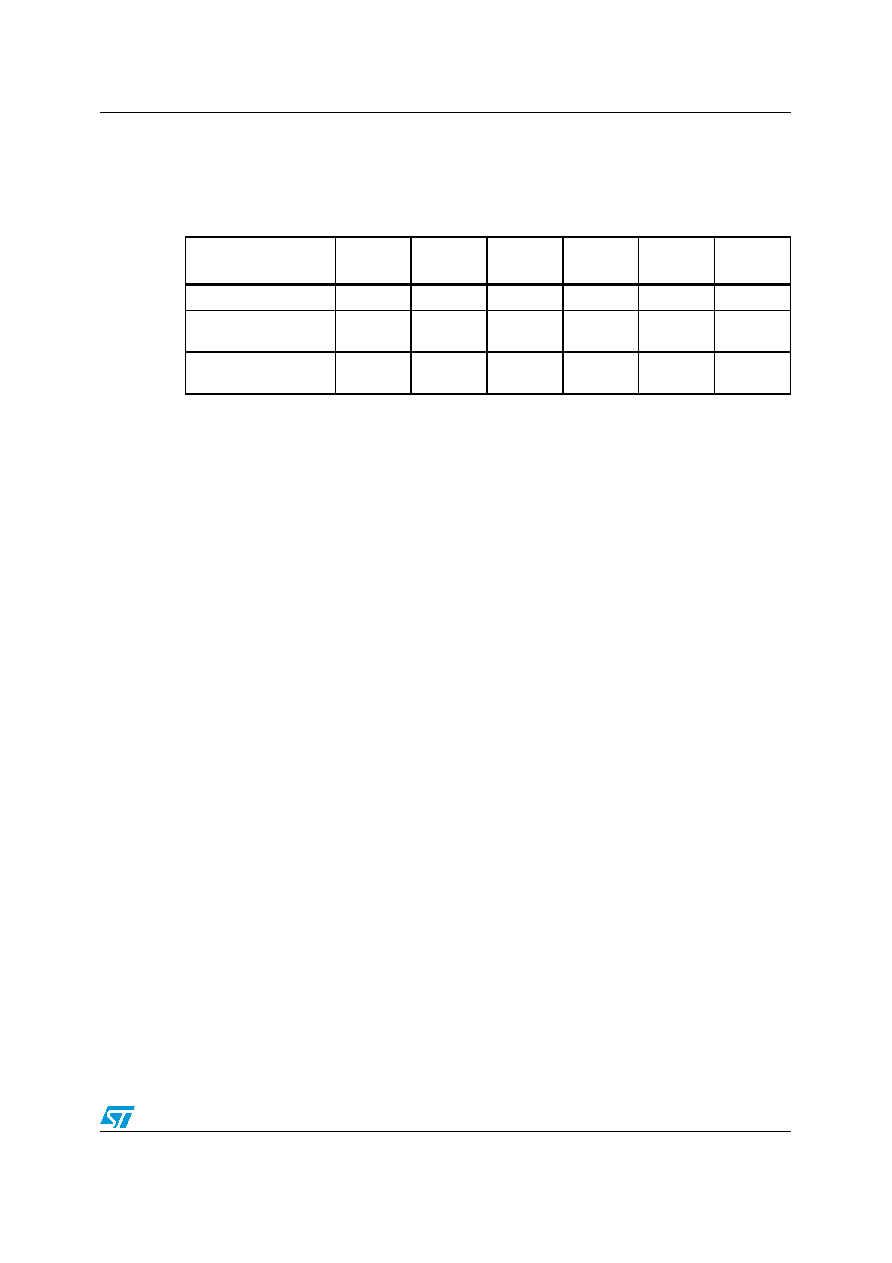

Table 23.

Timer GPIO use

Signal (direction)

TIMxC1

(in or out)

TIMxC2

(in or out)

TIMxC3

(in or out)

TIMxC4

(in or out)

TIMxCLK

(in)

TIMxMSK

(in)

Timer 1

PB6

PB7

PA6

PA7

PB0

PB5

Timer 2

(TIM_REMAPCy = 0)

PA0

PA3

PA1

PA2

PB5

PB0

Timer 2

(TIM_REMAPCy = 1)

PB1

PB2

PB3

PB4

PB5

PB0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| STP506C-2IW-012V | SINGLE COLOR DISPLAY CLUSTER, WHITE, 152.4 mm |

| SUGR47M | DUAL COLOR LED, RED/GREEN, 5 mm |

| SUR76D | SINGLE COLOR LED, RED, 3 mm |

| SUY17D | SINGLE COLOR LED, YELLOW, 3.9 mm |

| SY405T | SINGLE COLOR LED, AMBER, 2.7 mm |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| STM32WC-RFCKIT | 功能描述:Zigbee/802.15.4開(kāi)發(fā)工具 STM32W Low-Cost RF STM32F103 MCU Kit RoHS:否 制造商:Silicon Labs 產(chǎn)品:Development Kits 工具用于評(píng)估:EM35x 頻率:2.4 GHz 接口類型:USB 工作電源電壓: |

| STM32W-RFCKIT | 功能描述:開(kāi)發(fā)板和工具包 - 無(wú)線 STM32W RF CNTRL KIT STM32F103 USB JTAG RoHS:否 制造商:Arduino 產(chǎn)品:Evaluation Boards 工具用于評(píng)估:AT32UC3L 核心:AVR32 頻率: 接口類型:USB 工作電源電壓:5 V |

| STM3-3 | 制造商:RINO MECH.(GENGARELL 功能描述: |

| STM330 | 制造商:EnOcean GmbH 功能描述:Temperature energy harvester, 868MHz |

| STM330U | 制造商:EnOcean GmbH 功能描述:Temperature energy harvester, 315MHz 制造商:EnOcean GmbH 功能描述:Temperature energy harvester, 902MHz |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。