- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98145 > ST72F60E1M1 (STMICROELECTRONICS) 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDSO24 PDF資料下載

參數(shù)資料

| 型號: | ST72F60E1M1 |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDSO24 |

| 封裝: | 0.300 INCH, LEAD FREE, PLASTIC, SOP-24 |

| 文件頁數(shù): | 31/139頁 |

| 文件大小: | 1993K |

| 代理商: | ST72F60E1M1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當(dāng)前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁

Electrical characteristics

ST7260xx

126/139

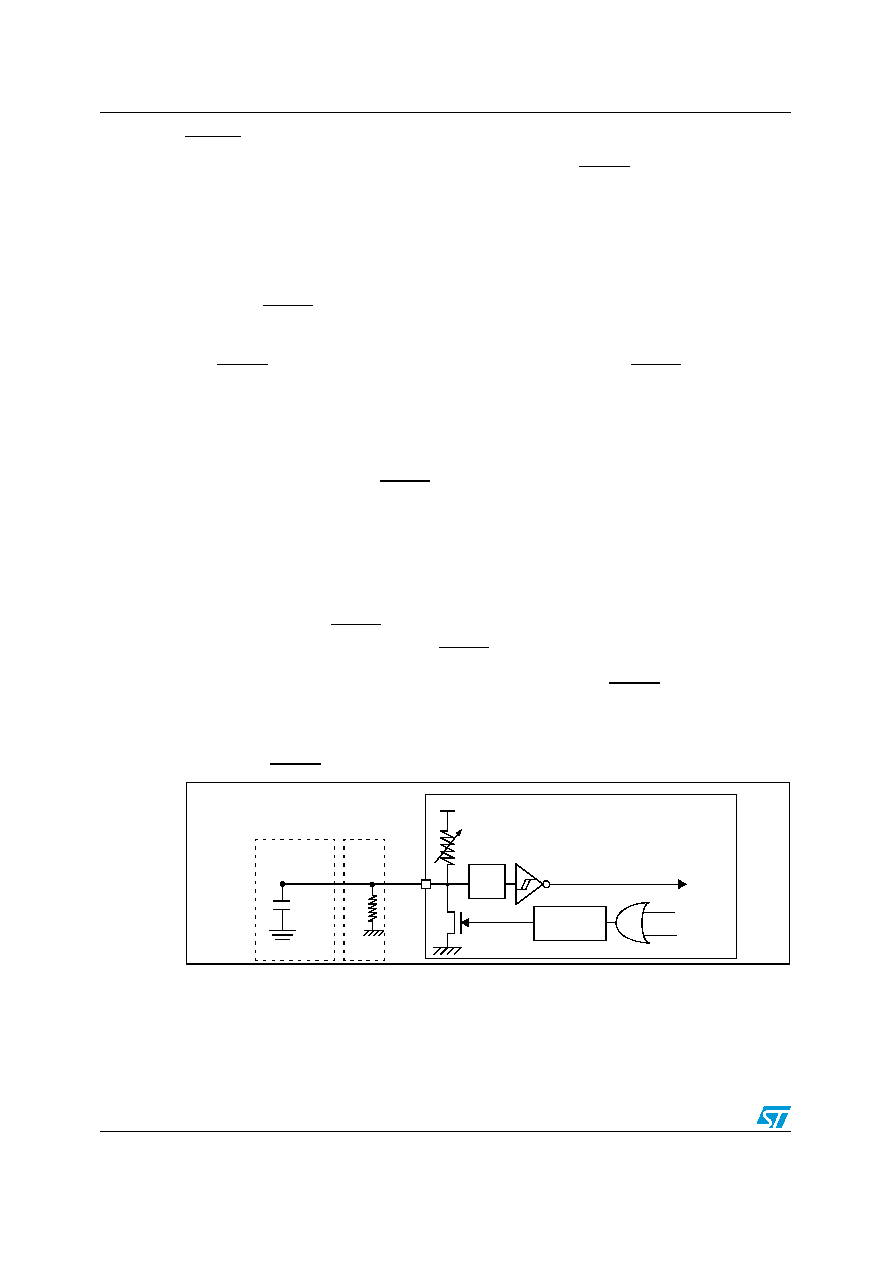

RESET pin protection when LVD is enabled

When the LVD is enabled, it is recommended to protect the RESET pin as shown in

Figure 64 and follow these guidelines:

1.

The reset network protects the device against parasitic resets.

2.

The output of the external reset circuit must have an open-drain output to drive the ST7

reset pad. Otherwise the device can be damaged when the ST7 generates an internal

reset (LVD or watchdog).

3.

Whatever the reset source is (internal or external), the user must ensure that the level

Otherwise the reset will not be taken into account internally.

4.

Because the reset circuit is designed to allow the internal RESET to be output in the

RESET pin, the user must ensure that the current sunk on the RESET pin (by an

external pull-up for example) is less than the absolute maximum value specified for

5.

When the LVD is enabled, it is mandatory not to connect a pull-up resistor. A 10nF pull-

down capacitor is recommended to filter noise on the reset line.

6.

In case a capacitive power supply is used, it is recommended to connect a 1M ohm

pull-down resistor to the RESET pin to discharge any residual voltage induced by this

capacitive power supply (this will add 5A to the power consumption of the MCU).

Tips when using the LVD:

●

Check that all recommendations related to reset circuit have been applied (see section

above)

●

Check that the power supply is properly decoupled (100 nF + 10 F close to the MCU).

Refer to AN1709. If this cannot be done, it is recommended to put a 100 nF + 1M Ohm

pull-down on the RESET pin.

●

The capacitors connected on the RESET pin and also the power supply are key to

avoiding any start-up marginality. In most cases, steps 1 and 2 above are sufficient for a

robust solution. Otherwise: Replace 10nF pull-down on the RESET pin with a 5 F to

20 F capacitor.

Figure 64.

RESET pin protection when LVD is enabled

0.01

μF

ST72XXX

PULSE

GENERATOR

Filter

RON

VDD

WATCHDOG

LVD RESET

INTERNAL

RESET

EXTERNAL

Required

1 M

Ω

Optional

(note 6)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST72F60K2DIE1 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, UUC |

| ST72F60K2DIE6 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, UUC |

| ST72F651AR6T1 | 8-BIT, FLASH, MICROCONTROLLER, PQFP64 |

| ST72P60E2M1 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO24 |

| ST7260E2M1/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO24 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST72F60E2M1 | 功能描述:8位微控制器 -MCU ST7262 Lo Spd USB 8B MCU RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| ST72F60K1U1 | 功能描述:8位微控制器 -MCU 8 BITS MICROCONTR RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| ST72F60K1U1TR | 功能描述:8位微控制器 -MCU ST7262 Lo Spd USB 8B MCU RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| ST72F60K2B1 | 功能描述:8位微控制器 -MCU 8 BITS MICROCONTR RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| ST72F60K2U1TR | 功能描述:8位微控制器 -MCU ST7262 Lo Spd USB 8B MCU RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。