- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372122 > SC28L202A1 (NXP Semiconductors N.V.) Dual universal asynchronous receiver/transmitter DUART PDF資料下載

參數(shù)資料

| 型號(hào): | SC28L202A1 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Dual universal asynchronous receiver/transmitter DUART |

| 中文描述: | 雙路通用異步接收器/發(fā)送器杜阿爾特 |

| 文件頁(yè)數(shù): | 28/77頁(yè) |

| 文件大小: | 531K |

| 代理商: | SC28L202A1 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)當(dāng)前第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)

Philips Semiconductors

Objective specification

SC28L202

Dual UART

2000 Feb 10

22

UART Registers

These registers are generally concerned with formatting,

transmitting and receiving data.

The user must exercise caution when changing the mode of running

receivers, transmitters, PBRG or counter/timers. The selected mode

will be activated immediately upon selection, even if this occurs

during the reception or transmission of a character. It is also

possible to disrupt internal controllers by changing modes at critical

times, thus rendering later transmission or reception faulty or

impossible.

An exception to this policy is switching from auto–echo or remote

loop back modes to normal mode. If the deselecting occurs just after

the receiver has sampled the stop bit (in most cases indicated by

the assertion of the channel’s RxRDY bit) and the transmitter is

enabled, the transmitter will remain in auto–echo mode until the end

of the transmission of the stop bit.

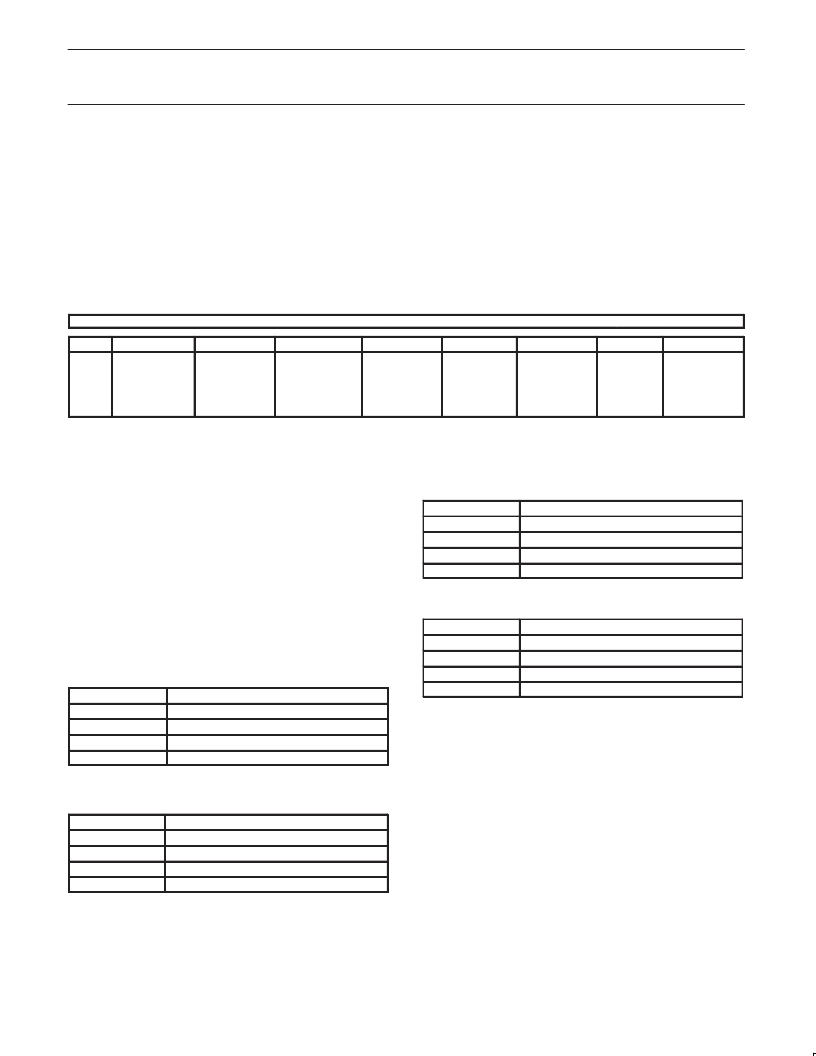

MR0 – Mode Register 0, A and B

MR0 can be accessed directly at H’20” and H’28” in the Extended section of the address map, or by means of the “MR Pointers” at the 0x00

and 0x08 address pointers used by legacy code.

(TEST 1)

(TEST 3)

Bit 7

Rx Watchdog

*

0 = Disable

1 = Enable

BIT 6

RxINT BIT 2

See Tables in

MR0

description

BIT (5:4)

TxINT (1:0)

See Table 13

BIT 3

FIFO Size

0 = 8 bytes

1 = 256

bytes

BIT 2

BAUD RATE

EXTENDED II

0 = NormaL

1 = Extend II

BIT 1

Reserved

Set to 0

BIT 0

BAUD RATE

EXTENDED 1

0 = Normal

1 = Extend

MR0 A, MR0

B, and

MR0 B[3:0]

are reserved

*This bit control is duplicated at MR0[7].

MR0[7] Fixed length Watchdog Timer

This bit controls the receiver watchdog timer. 0 = disable, 1 =

enable. When enabled, the watch dog timer will generate a receiver

interrupt if the receiver FIFO has not been accessed within 64 bit

times of the receiver 1X clock. This is used to alert the control

processor that data is in the RxFIFO that has not been read. This

situation may occur when the byte count of the last part of a

message is not large enough to generate an interrupt.

MR0[6]

– Bit 2 of receiver FIFO interrupt level. This bit along with Bit

6 of MR1 sets the fill level of the 8 byte FIFO that generates the

receiver interrupt.

MR0[6] and MR1[6]

Note that this control is split between MR0 and

MR1. This is for backward compatibility to the SC2692 and

SCN2681.

Table 3. Receiver FIFO Interrupt Fill Level

MR0(3)=0

MR0[6] MR1[6]

Interrupt Condition

00

1 or more bytes in FIFO (RxRDY)

01

3 or more bytes in FIFO

10

6 or more bytes in FIFO

11

8 bytes in FIFO (Rx FULL)

Table 4. Receiver FIFO Interrupt Fill Level

MR0(3)=1

MR0[6] MR1[6]

Interrupt Condition

00

1 or more bytes in FIFO (RxRDY)

01

128 or more bytes in FIFO

10

192 or more bytes in FIFO

11

256 bytes in FIFO (Rx FULL)

For the receiver these bits control the number of FIFO positions

filled when the receiver will attempt to interrupt. After the reset the

receiver FIFO is empty. The default setting of these bits cause the

receiver to attempt to interrupt when it has one or more bytes in it.

MR0[5:4] – Tx interrupt fill level.

Table 5. Transmitter FIFO Interrupt Fill Level

MR0(3)=0

MR0[5:4]

Interrupt Condition

00

8 bytes empty (Tx EMPTY)

01

4 or more bytes empty

10

6 or more bytes empty

11

1 or more bytes empty (TxRDY)

Table 6. Transmitter FIFO Interrupt Fill Level

MR0(3)=0

MR0[5:4]

Interrupt Condition

00

256 bytes empty (Tx EMPTY)

01

128 or more bytes empty

10

192 or more bytes empty

11

1 or more bytes empty (TxRDY)

For the transmitter these bits control the number of FIFO positions

empty when the receiver will attempt to interrupt. After the reset the

transmit FIFO has 8 bytes empty. It will then attempt to interrupt as

soon as the transmitter is enabled. The default setting of the MR0

bits (00) condition the transmitter to attempt to interrupt only when it

is completely empty. As soon as one byte is loaded, it is no longer

empty and hence will withdraw its interrupt request.

MR0[3] – FIFO Size

Selects between 8 or 256 byte FIFO structure

MR0[2:0] – Legacy Baud Rate Group Selection

These bits are used to select one of the six–baud rate groups.

See Table 13 for the group organization.

000 Normal mode

001 Extended mode I

100 Extended mode II

Other combinations of MR2[2:0] should not be used

NOTE:

MR0[3:0] are not used in channel B and should be set to 0.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SC28L202 | Dual universal asynchronous receiver/transmitter DUART |

| SC28L202A1B | Dual universal asynchronous receiver/transmitter DUART |

| SC28L202A1D | Dual universal asynchronous receiver/transmitter DUART |

| SC431CS8DE2 | Analog IC |

| SC431CS8DE3 | Analog IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SC28L202A1B | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Dual universal asynchronous receiver/transmitter DUART |

| SC28L202A1D | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Dual universal asynchronous receiver/transmitter DUART |

| SC28L202A1DGG | 功能描述:UART 接口集成電路 3-5V 2CH UART 3MBPS 256B FIFO RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| SC28L202A1DGG,112 | 功能描述:UART 接口集成電路 3-5V 2CH UART 3MBPS RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| SC28L202A1DGG,118 | 功能描述:UART 接口集成電路 3-5V 2CH UART 3MBPS RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。