- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄372112 > SAA7105H (NXP Semiconductors N.V.) Digital video encoder PDF資料下載

參數(shù)資料

| 型號(hào): | SAA7105H |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類(lèi): | 通用總線功能 |

| 英文描述: | Digital video encoder |

| 文件頁(yè)數(shù): | 37/71頁(yè) |

| 文件大小: | 354K |

| 代理商: | SAA7105H |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)當(dāng)前第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)

2004 Mar 04

37

Philips Semiconductors

Product specification

Digital video encoder

SAA7104H; SAA7105H

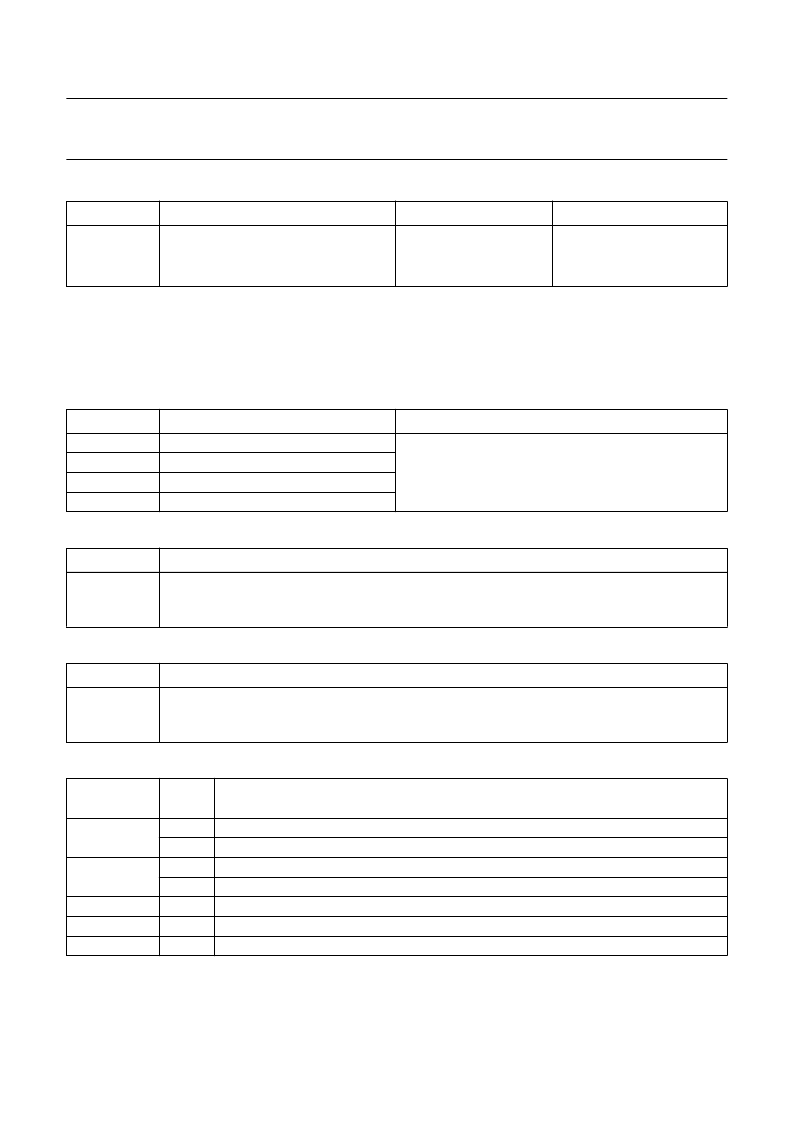

Table 48

Subaddresses 63H to 66H (four bytes to program subcarrier frequency)

Note

1.

Examples:

a) NTSC M: f

fsc

= 227.5, f

llc

= 1716

→

FSC = 569408543 (21F07C1FH).

b) PAL B/G: f

fsc

= 283.7516, f

llc

= 1728

→

FSC = 705268427 (2A098ACBH).

Table 49

Subaddresses 67H to 6AH

Table 50

Subaddresses 6CH and 6DH

Table 51

Subaddress 6DH

Table 52

Subaddress 6EH

DATA BYTE

DESCRIPTION

CONDITIONS

REMARKS

FSC0 to FSC3 f

fsc

= subcarrier frequency (in multiples

of line frequency); f

llc

= clock frequency

(in multiples of line frequency)

;

note 1

FSC3 = most significant byte;

FSC0 = least significant byte

DATA BYTE

DESCRIPTION

REMARKS

L21O0

L21O1

L21E0

L21E1

first byte of captioning data, odd field

second byte of captioning data, odd field

first byte of extended data, even field

second byte of extended data, even field

LSBs of the respective bytes are encoded immediately

after run-in and framing code, the MSBs of the respective

bytes have to carry the parity bit, in accordance with the

definition of line 21 encoding format.

DATA BYTE

DESCRIPTION

HTRIG

sets the horizontal trigger phase related to chip-internal horizontal input

values above 1715 (FISE = 1) or 1727 (FISE = 0) are not allowed; increasing HTRIG decreases

delays of all internally generated timing signals; the default value is 0

DATA BYTE

DESCRIPTION

VTRIG

sets the vertical trigger phase related to chip-internal vertical input

increasingVTRIGdecreasesdelaysofallinternallygeneratedtimingsignals,measuredinhalflines;

variation range of VTRIG = 0 to 31 (1FH); the default value is 0

DATA BYTE

LOGIC

LEVEL

DESCRIPTION

NVTRIG

0

1

0

1

values of the VTRIG register are positive

values of the VTRIG register are negative

encoder in normal operation mode; default after reset

output signal is forced to blanking level

selects the phase reset mode of the colour subcarrier generator; see Table 53

selects the delay on luminance path with reference to chrominance path; see Table 54

field length control; see Table 55

BLCKON

PHRES

LDEL

FLC

FSC

round

f

llc

f

2

32

×

=

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA7105H | Digital video encoder |

| SAA7108 | PC-CODEC |

| SAA7109 | PC-CODEC |

| SAA7108E | PC-CODEC |

| SAA7109E | PC-CODEC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA7105H/V1,518 | 功能描述:視頻 IC PC DENC WO MACROVISION LICENSE RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| SAA7105H/V1,557 | 功能描述:視頻 IC PC GRAPHICS 85MHZ RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| SAA7105HBG | 功能描述:視頻 IC PC GRAPHICS 85MHZ ENCODER RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| SAA7108 | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:PC-CODEC |

| SAA7108AE | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:HD-CODEC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。