- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372108 > SAA2501 (NXP Semiconductors N.V.) Digital Audio Broadcast DAB decoder PDF資料下載

參數(shù)資料

| 型號(hào): | SAA2501 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Digital Audio Broadcast DAB decoder |

| 中文描述: | 數(shù)字音頻廣播民建聯(lián)的解碼器 |

| 文件頁(yè)數(shù): | 16/52頁(yè) |

| 文件大小: | 206K |

| 代理商: | SAA2501 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)當(dāng)前第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)

January 1995

16

Philips Semiconductors

Preliminary specification

Digital Audio Broadcast (DAB) decoder

SAA2501

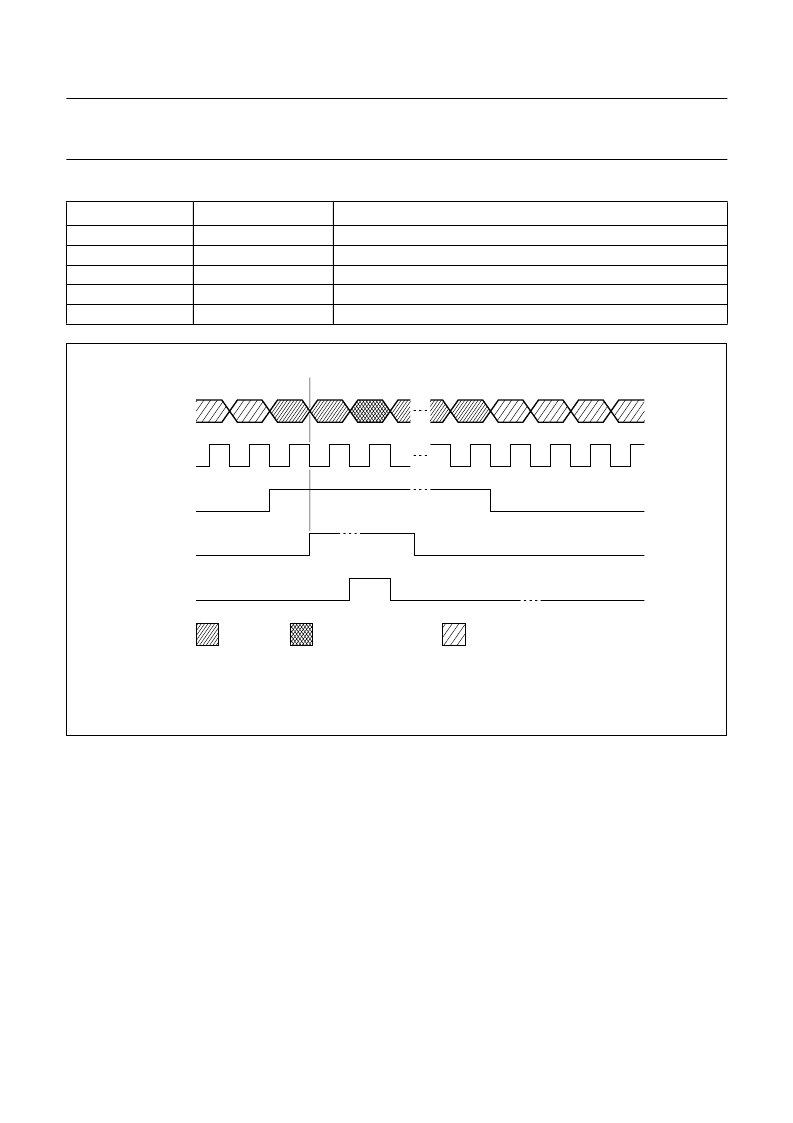

Table 8

Signals of coded data slave input interface

SIGNAL

DIRECTION

FUNCTION

CDS

CDSEF

CDSCL

CDSWA

CDSSY

input

input

input

input

input

ISO/MPEG or EU147 coded input data (slave input)

coded data (slave input) error flag

coded data (slave input) bit clock

coded data (slave input) burst window signal

coded data (slave input) frame sync

Fig.8 Input data serial transfer format (slave input).

CDSSY indicates frame start during valid data.

handbook, full pagewidth

CDSWA

CDSCL

CDSSY

MGB496

CDSEF

CDS

valid data

valid but unreliable data

invalid data

frame start

1 unreliable data bit (example)

CDS is the SAA2501 input data bitstream. Data clock

CDSCL must have a frequency equal to or higher than the

bit rate. The maximum CDSCL frequency is 768 kHz. Error

flag CDSEF is handled in the same way as CDMEF is

handled for the master input (in Fig.8, one unreliable data

bit is shown as an example). The value of CDSEF is

neglected for those bits where CDSWA is LOW. Window

signal CDSWA being HIGH indicates valid data; in this

way, burst input data is allowed. The constraints for the

ability to use ‘burst signals’ are explained later in this

Section 7.17.2. Frame sync signal CDSSY indicates the

start of each input data frame. CDSSY is synchronous with

CDSCL. CDSSY may be present or not: as described later

in this Section 7.17.2. The first valid CDS bit after a leading

edge of CDSSY is interpreted to be the first frame bit.

The minimum time for CDSSY to stay HIGH is one CDSCL

period; the maximum HIGH period is constrained by the

requirement that CDSSY must be LOW at least during one

CDSCL period per frame (a leading edge, i.e. a frame start

indication, must be present every frame). Leading edges

of CDSSY can occur while CDSWA is HIGH, as in Fig.8.

Alternatively, a situation as shown in Fig.9 is also allowed,

where CDSSY has a leading edge while CDSWA is LOW,

i.e. during invalid data. The first CDS bit after CDSWA

going HIGH is now interpreted to be the first frame bit.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA2501H | Digital Audio Broadcast DAB decoder |

| SAA2502 | ISO/MPEG Audio Source Decoder |

| SAA2502H | ISO/MPEG Audio Source Decoder |

| SAA2503 | MPEG2 audio decoder(MPEG2 音頻譯碼器) |

| SAA2503HT | MPEG2 audio decoder |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA2501H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Digital Audio Broadcast DAB decoder |

| SAA2501HB-S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Digital Audio Decoder & Support |

| SAA2502 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:ISO/MPEG Audio Source Decoder |

| SAA2502H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:ISO/MPEG Audio Source Decoder |

| SAA2503 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:MPEG2 audio decoder |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。