- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄192300 > S29XS064R0PBHW010 (SPANSION LLC) 4M X 16 FLASH 1.8V PROM, 80 ns, PBGA44 PDF資料下載

參數(shù)資料

| 型號: | S29XS064R0PBHW010 |

| 廠商: | SPANSION LLC |

| 元件分類: | PROM |

| 英文描述: | 4M X 16 FLASH 1.8V PROM, 80 ns, PBGA44 |

| 封裝: | 7.50 X 5 MM, LEAD FREE, FBGA-44 |

| 文件頁數(shù): | 23/65頁 |

| 文件大小: | 2116K |

| 代理商: | S29XS064R0PBHW010 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁

This document contains information on one or more products under development at Spansion Inc. The information is intended to help you evaluate this product. Do not design in

this product without contacting the factory. Spansion Inc. reserves the right to change or discontinue work on this proposed product without notice.

Publication Number S29VS_XS064R_00

Revision 06

Issue Date July 22, 2011

Distinctive Characteristics

Single 1.8 volt read, program and erase

(1.7 to 1.95 volt)

VersatileIO Feature

– Device generates data output voltages and tolerates data input

voltages as determined by the voltage on the VCCQ pin

– 1.8 V compatible I/O signals

Address and Data Interface Options

– Address and Data Multiplexed for reduced I/O count

(ADM) S29VS-R

– Address-High, Address-Low, Data Multiplexed for minimum I/O

count (AADM) S29XS-R

Simultaneous Read/Write operation

– Data can be continuously read from one bank while executing

erase/program functions in other bank

– Zero latency between read and write operations

Burst length

– Continuous linear burst

– 8/16 word linear burst with wrap around

Secured Silicon Sector region

– 256 words accessible through a command sequence, 128 words for

the Factory Secured Silicon Sector and 128 words for the Customer

Secured Silicon Sector.

Sector Architecture

– Four 8 kword sectors in upper-most address range

– One hundred twenty-seven 32 kword sectors

– Four banks

Security Features

Dynamic Protection Bit (DYB)

– A command sector protection method to lock combinations of

individual sectors to prevent program or erase operations within that

sector

– Sectors can be locked and unlocked in-system at VCC level

Hardware Sector Protection

– All sectors locked when VPP = VIL

Handshaking feature

– Provides host system with minimum possible latency by monitoring

RDY

Supports Common Flash Memory

Interface (CFI)

Manufactured on 65 nm MirrorBit process technology

Cycling endurance: 100,000 cycles per sector typical

Data retention: 10 years typical

Data# Polling and toggle bits

– Provides a software method of detecting program and erase

operation completion

Erase Suspend/Resume

– Suspends an erase operation to read data from, or program data to,

a sector that is not being erased, then resumes the erase operation

Program Suspend/Resume

– Suspends a programming operation to read data from a sector other

than the one being programmed, then resume the programming

operation

Packages

– 44-ball Very Thin FBGA

Performance Characteristics

S29VS/XS-R MirrorBit

Flash Family

S29VS064R, S29XS064R

64 Megabit (4M x 16-bit), CMOS 1.8 Volt-Only Simultaneous

Read/Write, Multiplexed, Burst Mode Flash Memory

Data Sheet (Advance Information)

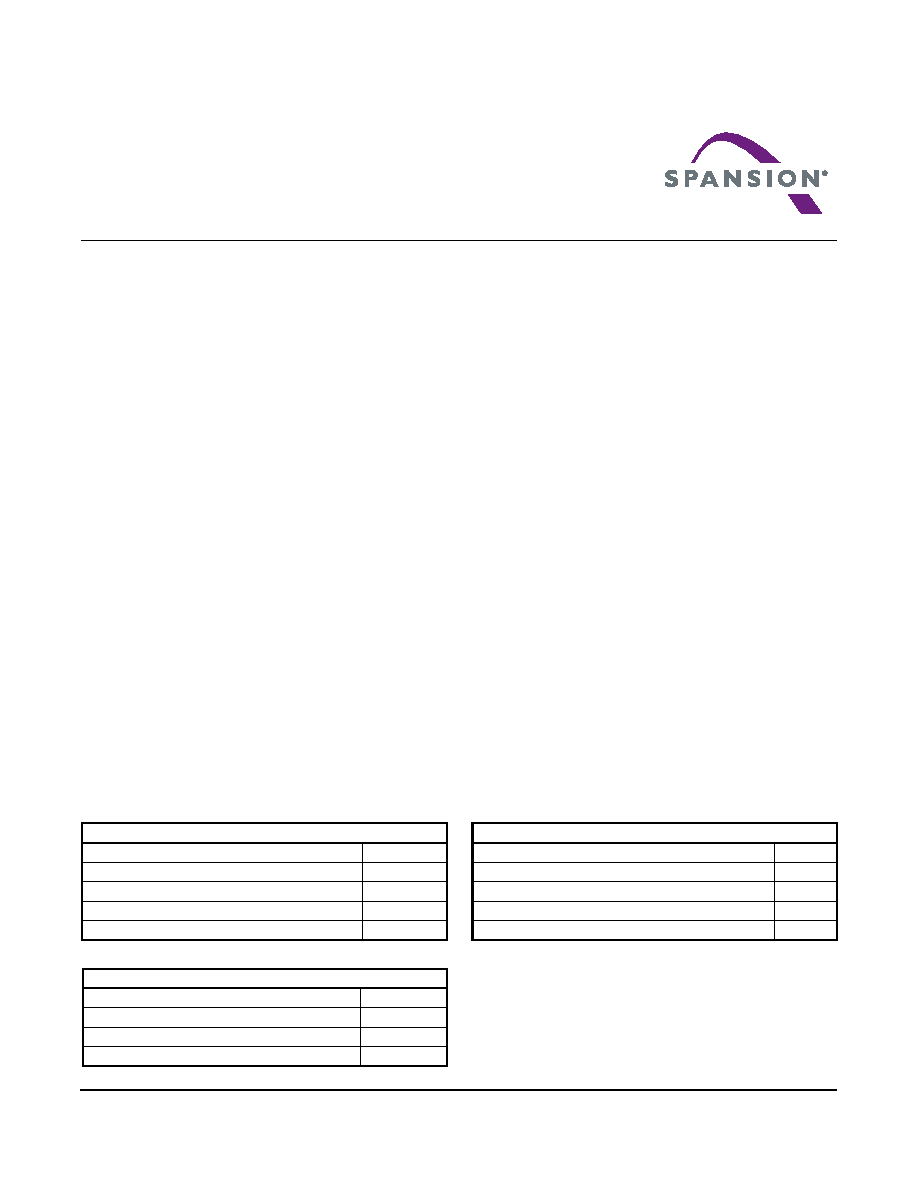

Read Access Times

Speed Option (MHz)

108

Max. Synch. Latency, ns (tIACC)

80

Max. Synch. Burst Access, ns (tBACC)

7.6

Max. Asynch. Access Time, ns (tACC)80

Max OE# Access Time, ns (tOE)15

Current Consumption (typical values)

Continuous Burst Read @ 108 MHz

32 mA

Simultaneous Operation @ 108 MHz

71 mA

Program/Erase

30 mA

Standby Mode

20 A

Typical Program & Erase Times

Single Word Programming

170 s

Effective Write Buffer Programming (VCC) Per Word

14.1 s

Effective Write Buffer Programming (VPP) Per Word

9 s

Sector Erase (8 kword Sector)

350 ms

Sector Erase (32 kword Sector)

800 ms

相關PDF資料 |

PDF描述 |

|---|---|

| S2C3R-1-12-H | 4000 MHz - 12000 MHz RF/MICROWAVE SGL POLE DOUBLE THROW SWITCH, 2 dB INSERTION LOSS |

| S2C5R-1-12-RC | 4000 MHz - 18000 MHz RF/MICROWAVE SGL POLE DOUBLE THROW SWITCH, 2.8 dB INSERTION LOSS |

| S2H3R-1H | 10 MHz - 1000 MHz RF/MICROWAVE SGL POLE DOUBLE THROW SWITCH, 1.2 dB INSERTION LOSS |

| S2L1R-RC | 1000 MHz - 2000 MHz RF/MICROWAVE SGL POLE DOUBLE THROW SWITCH, 0.9 dB INSERTION LOSS |

| S2L7R-1-RC | 1000 MHz - 18000 MHz RF/MICROWAVE SGL POLE DOUBLE THROW SWITCH, 2.9 dB INSERTION LOSS |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| S-29XX0A | 制造商:SII 制造商全稱:Seiko Instruments Inc 功能描述:CMOS SERIAL EEPROM |

| S-29XX1A | 制造商:SII 制造商全稱:Seiko Instruments Inc 功能描述:CMOS SERIAL EEPROM |

| S-29ZX30A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Serial 3-wire EEPROMs |

| S2A | 功能描述:撥動開關 ON-NONE-ON SPDT SOLDER LUG RoHS:否 制造商:C&K Components 觸點形式:DPDT 開關功能:ON - ON - ON 電流額定值: 電壓額定值 AC:20 V 電壓額定值 DC:20 V 功率額定值:0.4 VA 端接類型:V-Bracket 安裝風格: 端子密封:Epoxy 觸點電鍍:Gold 照明:Not Illuminated |

| S-2A | 制造商:Nihon Kaiheiki Ind Co Ltd 功能描述:30V 50000(@BIv) / 25000(dCIv) bL +85 -30 30mm 18mm 45.5mm Bulk 制造商:Nihon Dempa Kogyo Co (NDK) 功能描述:Switch, toggle, solder terminal, minitur |

發(fā)布緊急采購,3分鐘左右您將得到回復。