- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378161 > RM5231 (PMC-Sierra, Inc.) RM5231⑩ Microprocessor with 32-Bit System Bus Data Sheet Released PDF資料下載

參數(shù)資料

| 型號(hào): | RM5231 |

| 廠商: | PMC-Sierra, Inc. |

| 英文描述: | RM5231⑩ Microprocessor with 32-Bit System Bus Data Sheet Released |

| 中文描述: | RM5231⑩微處理器與32位系統(tǒng)總線的數(shù)據(jù)資料發(fā)布 |

| 文件頁(yè)數(shù): | 17/39頁(yè) |

| 文件大?。?/td> | 630K |

| 代理商: | RM5231 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer

’

s Internal Use

Document ID: PMC-2002165, Issue 1

17

RM5231

Microprocessor with 32-bit System Bus Data Sheet

Released

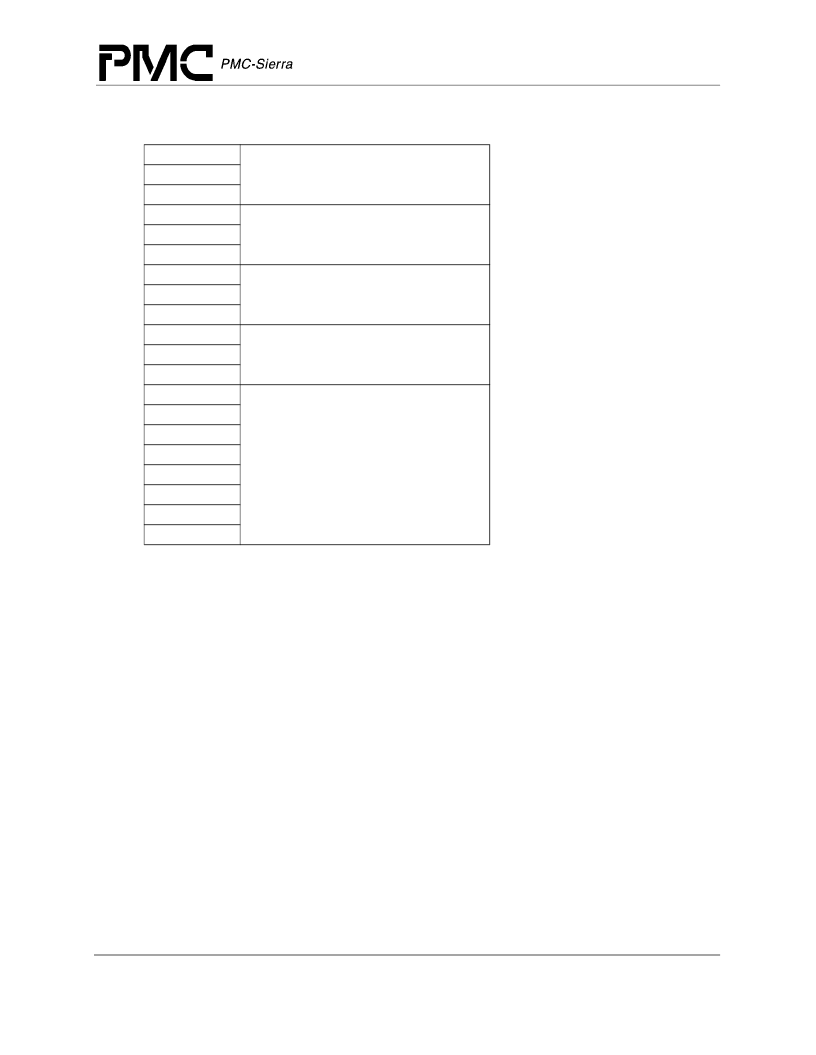

Figure 5 Kernel Mode Virtual Addressing (32-bit)

Kernel virtual address space

(kseg3)

Mapped, 0.5 GB

0xE0000000

Supervisor virtual address space

(ksseg)

Mapped, 0.5 GB

0xC0000000

Uncached kernel physical address space

(kseg1)

Unmapped, 0.5 GB

0xA0000000

Cached kernel physical address space

(kseg0)

Unmapped, 0.5 GB

0x80000000

User virtual address space

(kuseg)

Mapped, 2.0 GB

3.14 Joint TLB

For fast virtual-to-physical address translation, the RM5231 uses a large, fully associative TLB

that maps 96 virtual pages to their corresponding physical addresses. As indicated by its name, the

joint TLB (JTLB) is used for both instruction and data translations. The JTLB is organized as 48

pairs of even-odd entries, and maps a virtual address and address space identifier into the large, 64

GB physical address space.

Two mechanisms are provided to assist in controlling the amount of mapped space and the

replacement characteristics of various memory regions. First, the page size can be configured, on a

per-entry basis, to use page sizes in the range of 4 KB to 16 MB (in multiples of 4). The CP0 Page

Mask register is loaded with the desired page size of a mapping, and that size is stored into the

TLB along with the virtual address when a new entry is written. Thus, operating systems can

create special purpose maps; for example, an entire frame buffer can be memory mapped using

only one TLB entry.

The second mechanism controls the replacement algorithm when a TLB miss occurs. The

RM5231 provides a random replacement algorithm to select a TLB entry to be written with a new

mapping. However, the processor also provides a mechanism whereby a system specific number of

mappings can be locked into the TLB, thereby avoiding random replacement. This mechanism

allows the operating system to guarantee that certain pages are always mapped for performance

reasons and for deadlock avoidance. This mechanism also facilitates the design of real-time

systems by allowing deterministic access to critical software.

0xFFFFFFFF

0xDFFFFFFF

0xBFFFFFFF

0x9FFFFFFF

0x7FFFFFFF

0x00000000

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RM5231-200-Q | RM5231⑩ Microprocessor with 32-Bit System Bus Data Sheet Released |

| RM5231-250-Q | RM5231⑩ Microprocessor with 32-Bit System Bus Data Sheet Released |

| RM5231A | RM5231A⑩ Microprocessor with 32-Bit System Bus Data Sheet Preliminary |

| RM5231A-250-H | RM5231A⑩ Microprocessor with 32-Bit System Bus Data Sheet Preliminary |

| RM5231A-300-H | RM5231A⑩ Microprocessor with 32-Bit System Bus Data Sheet Preliminary |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RM5231-150Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Microprocessor |

| RM5231-150Q-C001 | 制造商:PMC-Sierra 功能描述: |

| RM5231-200Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Microprocessor |

| RM5231-225Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Microprocessor |

| RM5231-250Q | 制造商:QED 功能描述:Microprocessor, 64 Bit, 128 Pin, Plastic, QFP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。