- 您現(xiàn)在的位置:買賣IC網 > PDF目錄370028 > PXA255 (Intel Corp.) PXA255 Processor PDF資料下載

參數(shù)資料

| 型號: | PXA255 |

| 廠商: | Intel Corp. |

| 英文描述: | PXA255 Processor |

| 中文描述: | PXA255處理器 |

| 文件頁數(shù): | 16/40頁 |

| 文件大小: | 1191K |

| 代理商: | PXA255 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

Package Information

16

Intel PXA255 Processor

Electrical, Mechanical, and Thermal Specification

TEXTAL

IA

32 kHz crystal output.

No external caps are required.

Note [2]

Note [2]

L_DD[12]/

GPIO[70]

ICOCZ

LCD display data.

(output) Transfers pixel information

from the LCD controller to the external LCD panel.

RTC clock.

(output) Real time clock 1 Hz tick.

Pulled High -

Note[1]

Note [3]

L_DD[13]/

GPIO[71]

ICOCZ

LCD display data.

(output) Transfers the pixel

information from the LCD controller to the external LCD

panel.

3.6864 MHz clock.

(output) Output from 3.6864 MHz

oscillator.

Pulled High -

Note[1]

Note [3]

L_DD[14]/

GPIO[72]

ICOCZ

LCD display data.

(output) Transfers pixel information

from the LCD controller to the external LCD panel.

32 kHz clock.

(output) Output from the 32 kHz oscillator.

Pulled High -

Note[1]

Note [3]

48MHz/GP[7]

ICOCZ

48 MHz clock.

(output) Peripheral clock output derived

from the PLL.

NOTE:

This clock is only generated when the USB unit

clock enable is set.

Pulled High -

Note[1]

Note [3]

RTCCLK/

GP[10]

ICOCZ

Real time clock.

(output) 1 Hz output derived from the

32 kHz or 3.6864 MHz output.

Pulled High -

Note[1]

Note [3]

3.6MHz/GP[11] ICOCZ

3.6864 MHz clock.

(output) Output from 3.6864 MHz

oscillator.

Pulled High -

Note[1]

Note [3]

32kHz/GP[12]

ICOCZ

32 kHz clock.

(output) Output from the 32 kHz oscillator.

Pulled High -

Note[1]

Note [3]

Miscellaneous Pins

BOOT_SEL

[2:0]

IC

Boot select pins.

(input)

Indicates type of boot device.

Input

Input

PWR_EN

OC

Power Enable for the power supply.

(output) When

negated, it signals the power supply to remove power to

the core because the system is entering sleep mode.

Driven High

Driven low while

entering sleep

mode. Driven high

when sleep exit

sequence begins.

nBATT_FAULT

IC

Main Battery Fault.

(input) Signals that main battery is

low or removed. Assertion causes PXA255 processor

processor to enter sleep mode or force an imprecise data

exception, which cannot be masked. PXA255 processor

will not recognize a wake-up event while this signal is

asserted. Minimum assertion time for nBATT_FAULT is 1

ms.

Input

Input

nVDD_FAULT

IC

VDD Fault.

(input) Signals that the main power source is

going out of regulation. nVDD_FAULT causes the

PXA255 processor to enter sleep mode or force an

imprecise data exception, which cannot be masked.

nVDD_FAULT is ignored after a wake-up event until the

power supply timer completes (approximately 10 ms).

Minimum assertion time for nVDD_FAULT is 1 ms.

Input

Input

nRESET

IC

Hard reset.

(input) Level -sensitive input used to start the

processor from a known address. Assertion terminates

the current instruction abnormally and causes a reset.

When nRESET is driven high, the processor starts

execution from address 0. nRESET must remain low until

the power supply is stable and the internal 3.6864 MHz

oscillator has stabilized.

Input

Input. Driving low

during sleep will

cause normal

reset sequence

and exit from sleep

mode.

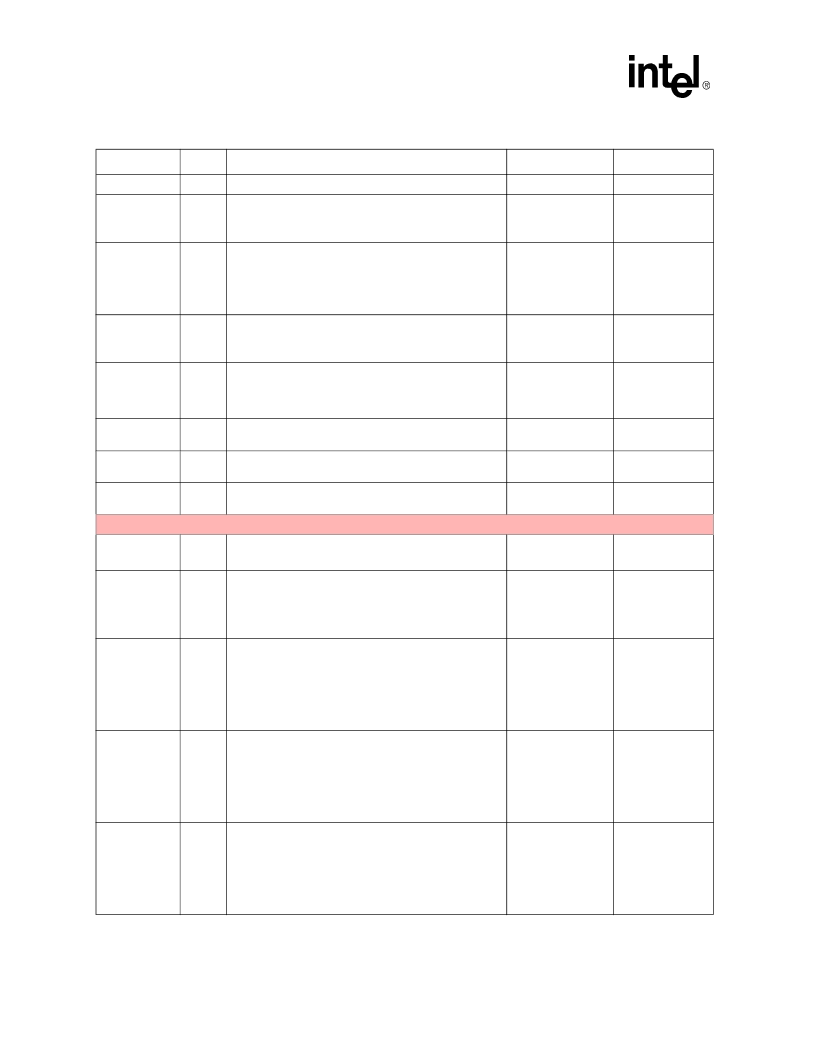

Table 3. Pin and Signal Descriptions for the PXA255 Processor (Sheet 8 of 9)

Pin Name

Type

Signal Descriptions

Reset State

Sleep State

相關PDF資料 |

PDF描述 |

|---|---|

| PXA270 | Electrical, Mechanical, and Thermal Specification |

| PXAC37 | XA 16-bit microcontroller family 32K/1024 OTP CAN transport layer controller 1 UART, 1 SPI Port, CAN 2.0B, 32 CAN ID Filters, transport layer co-proce |

| PXB16050U | NPN microwave power transistor |

| PY08-02 | INDUSTRIERELAIS FASSUNG PCB |

| PY08-02186697 | SOCKET PCB |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| PXA25VC22RMH70TP | 制造商:United Chemi-Con Inc 功能描述:Cap Aluminum 22uF 25V 20% (8 X 6.7mm) SMD 0.05 Ohm 1800mA 2000 hr 105°C T/R |

| PXA270 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Electrical, Mechanical, and Thermal Specification |

| PXA300 | 制造商:Marvell 功能描述: |

| PXA310 | 制造商:MARVELL 制造商全稱:MARVELL 功能描述:Rich Multimedia with Scalable Performance up to 624 MHz for Cost-Effective and Power-Effi cient Secure 3.5G Smartphones |

| PXA320 | 制造商:MARVELL 制造商全稱:MARVELL 功能描述:Cost-Effective, Scalable Performance up to 806 MHz for Power-Efficient, High-End Multimedia Handsets, Embedded Solutions, and Enterprise-Class Devices |

發(fā)布緊急采購,3分鐘左右您將得到回復。