- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370013 > PP155 Telecommunication IC PDF資料下載

參數(shù)資料

| 型號: | PP155 |

| 英文描述: | Telecommunication IC |

| 中文描述: | 通信集成電路 |

| 文件頁數(shù): | 20/31頁 |

| 文件大小: | 600K |

| 代理商: | PP155 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當(dāng)前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

20

Altera Corporation

Specifications

PPP Packet Processor 155 Mbps MegaCore Function (PP155) User Guide

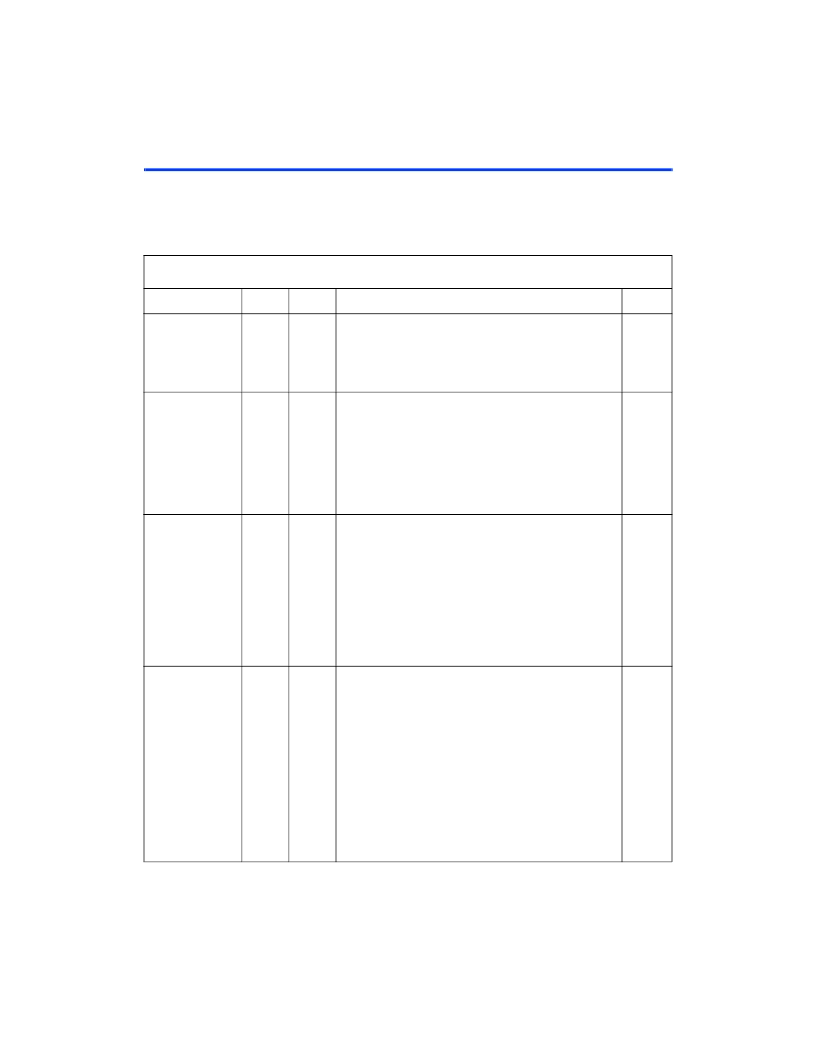

RX Register Description

The following tables describe the registers for the receiver section of the

PP155.

RX_CTRL - Receive Control Register - ’h00

Field

Bits

Access

Function

Default

REALIGN

5

RWSC

1: Forces aligner to try new alignment

Writing a 1 to this bit (note that it always reads as 0) forces

the byte aligner to try a new alignment. This bit is ignored if

align is 0.

0

ALIGN

4

RW

0: Byte alignment disabled.

1: Byte alignment enabled.

If set, the aligner monitors the error rate to determine if the

PPP bytes are aligned to mrxdat. If data are not aligned, it

shifts the data on mrxdat to attempt to align the data. If

cleared, the PPP bytes are assumed to be aligned to

mrxdat.

0

CRCLEN

3

RW

0: CRC-CCITT mode

1: CRC-32 mode

If set, the receiver computes syndromes for received

packets using the CRC-32 polynomial, if cleared, the CRC-

CCITT 16-bit polynomial. The syndrome is always

computed and checked. Packets with bad syndromes (i.e.

with errors) are not discarded, but are counted in the

Receive FCS Error Count register and marked as erroneous

when sent to the Atlantic interface.

0

SCRAMEN

2

RW

Enable descrambling of transmit frame and descrambling of

the receive frame.

This causes the received data stream to be descrambled

using the x^43+1 scrambling polynomial. The bits are

descrambled using the most significant (higher-numbered)

bit first. All bits, including flags, the body of the packet, and

the FCS are scrambled. The descrambling process is self-

synchronizing. The descrambler is not reset by the enable

bit and will therefore synchronize the state with the received

data stream while the enable is cleared. It should, therefore,

be set to its desired value and at least 43 bits of data should

be received before turning on the enable bit.

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PP5005 | POWER SUPPLY BENCH 0-15V 1A |

| PP5006 | POWER SUPP BENCH 0-30V 0.5A |

| PP5007 | POWER SUPP BENCH 5 & +/- 12V |

| PP5017 | PSU BENCH 3 O/P |

| PPA-1006 | Operational Amplifier |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PP15-52-10.0A-OB | 制造商:Sensata Technologies 功能描述:Circuit Breaker Magnetic Circuit Protectors 1Pole 10A |

| PP15-52-15.0A-OB | 制造商:Airpax 功能描述: 制造商:Sensata Technologies 功能描述:PP15-52-15.0A-OB /POLE # 1 /PROD FAMILY: 0213 |

| PP15-52-7.50A-XX | 制造商:Sensata Technologies 功能描述:1 Pole |

| PP15-59-.100A-XX | 制造商:Airpax 功能描述:CIRCUIT BREAKER 制造商:Sensata Technologies 功能描述:Circuit Breaker Magnetic Circuit Protectors 1Pole 0.1A |

| PP15-59-.500A-OC-S | 制造商:Sensata Technologies 功能描述:Circuit Breaker Magnetic Circuit Protectors 1Pole 0.5A |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。