- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369960 > PDI1394L21BP (NXP SEMICONDUCTORS) 1394 full duplex AV link layer controller PDF資料下載

參數(shù)資料

| 型號(hào): | PDI1394L21BP |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 1394 full duplex AV link layer controller |

| 中文描述: | 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP100 |

| 封裝: | 14 X 14 MM, 1 MM HEIGHT, PLASTIC, SOT-386-1, TQFP-100 |

| 文件頁數(shù): | 7/42頁 |

| 文件大小: | 233K |

| 代理商: | PDI1394L21BP |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

Philips Semiconductors

Preliminary data

PDI1394P23

2-port/1-port 400 Mbps physical layer interface

2001 Sep 06

7

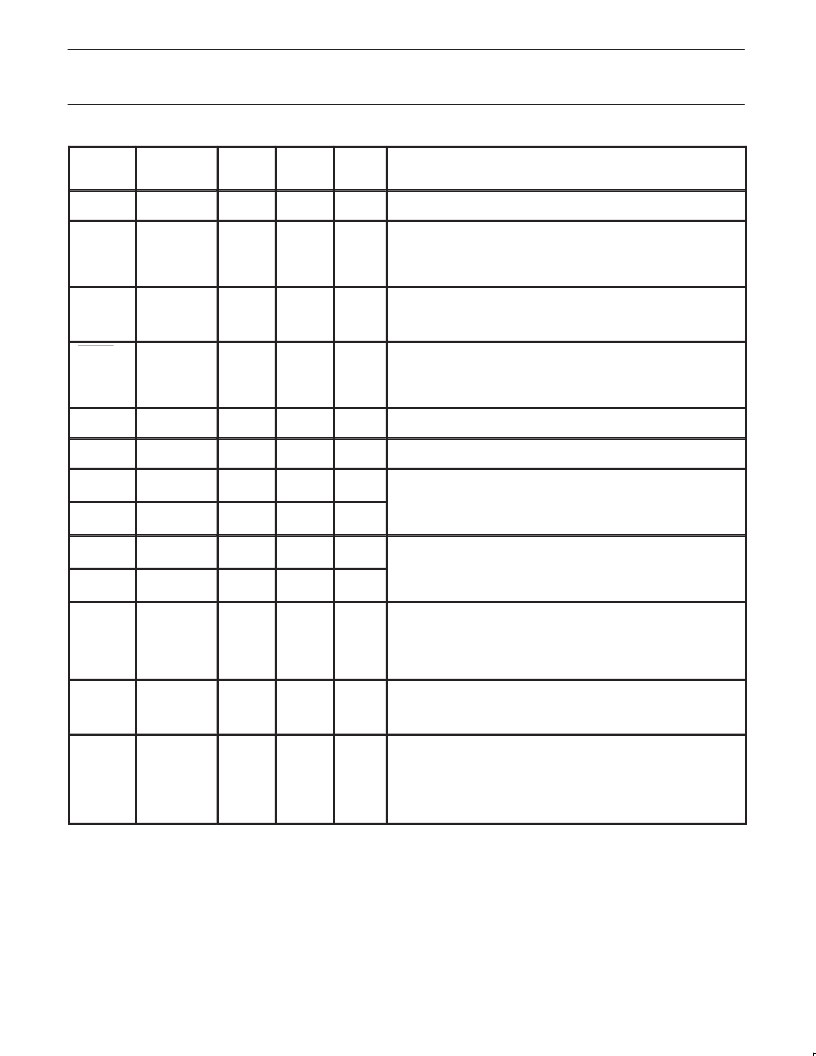

Name

Description

I/O

LFBGA

Ball

Numbers

LQFP

Pin

Numbers

Pin Type

PLLGND

Supply

57, 58

E1, D3

—

PLL circuit ground terminals. These terminals should be tied together to

the low impedance circuit board ground plane.

PLLV

DD

Supply

56

D1, D4

—

PLL circuit power terminals. A combination of high frequency decoupling

capacitors near each terminal are suggested, such as paralleled 0.1

μ

F

and 0.001

μ

F. This supply terminals is separated from DV

DD

and AV

DD

internal to the device to provide noise isolation. They should be tied at a

low impedance point on the circuit board.

R0

R1

Bias

40

41

D5

A4

—

Current setting resistor pins. These pins are connected to an external

resistor to set the internal operating currents and cable driver output

currents. A resistance of 6.34 k

±

1% is required to meet the IEEE

1394–1995 Std. output voltage limits.

RESET

CMOS 5V tol

53

C1

I

Logic reset input. Asserting this terminal low resets the internal logic. An

internal pull-up resistor to V

is provided so only an external

delay capacitor is required for proper power-up operation. For more

information, refer to Section 17.2. This input is otherwise a standard

Schmitt logic input, and can also be driven by an open-drain type driver.

SYSCLK

CMOS

2

H2

O

System clock output. Provides a 49.152 MHz clock signal, synchronized

with data transfers, to the LLC.

TEST0

CMOS

29

C8

I

Test control input. This input is used in manufacturing tests of the

PDI1394P23. For normal use, this terminal should be tied to GND.

TPA0+,

TPA1+

Cable

37

46

B5

B3

I/O

Twisted-pair cable A differential signal terminals. Board traces from each

pair of positive and negative differential signal terminals should be kept

matched and as short as possible to the external load resistors and to

the cable connector. TPA1+ and TPA1– can be left unconnected if the

TWOPORT pin is tied to DGND.

TPA0–,

TPA1–

Cable

36

45

B6

A3

I/O

TPB0+,

TPB1+

Cable

35

44

C6

C4

I/O

Twisted-pair cable B differential signal terminals. Board traces from each

pair of positive and negative differential signal terminals should be kept

matched and as short as possible to the external load resistors and to

the cable connector. TPB1+ and TPB1– can be left unconnected if the

TWOPORT pin is tied to DGND.

TPB0–,

TPB1–

Cable

34

43

A7

B4

I/O

TPBIAS0,

TPBIAS1

Cable

38

47

A6

A2

I/O

Twisted-pair bias output. This provides the 1.86V nominal bias voltage

needed for proper operation of the twisted-pair cable drivers and

receivers, and for signaling to the remote nodes that there is an active

cable connection. These terminals must be decoupled with a

0.3

μ

F–1

μ

F capacitor to ground. TPBIAS1 can be left unconnected if

the TWOPORT pin is tied to DGND.

TWOPORT

27

D7

One/two port selector pin. This pin should be tied to DV

for two port

operation and tied to DGND for one port operation. When tied to DV

DD

,

both ports 0 and 1 are operational. When tied to DGND, port 0 is

operational and port 1 is disabled.

XI

XO

Crystal

59

60

E2

E3

—

Crystal oscillator inputs. These terminals connect to a 24.576 MHz

parallel resonant fundamental mode crystal. The optimum values for the

external shunt capacitors are dependent on the specifications of the

crystal used. Can also be driven by an external clock generator (leave

XO unconnected in this case and start supplying the external clock

before resetting the PDI1394P23). For more information, refer to

Section 17.5

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PDL-TTL-7-1 | Programmable Delay Line |

| PDL-TTL-7-14 | Programmable Delay Line |

| PDL-TTL-7-15 | Programmable Delay Line |

| PDL-TTL-7-2 | Programmable Delay Line |

| PDL-TTL-7-20 | Programmable Delay Line |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PDI1394L40 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:1394 enhanced AV link layer controller |

| PDI1394L40BE | 制造商:NXP Semiconductors 功能描述:1 CHANNEL(S), 400M BPS, SERIAL COMM CONTROLLER, PQFP144 |

| PDI1394L40BE,518 | 功能描述:視頻 IC 1394 A/V LINK LAYER RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| PDI1394L40BE,551 | 制造商:NXP Semiconductors 功能描述:1394 A/V LINK LAYER - Trays |

| PDI1394L40BE,557 | 功能描述:視頻 IC DO NOT USE ORDER -S OR -T PART RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。