- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369960 > PDI1394L21BP (NXP SEMICONDUCTORS) 1394 full duplex AV link layer controller PDF資料下載

參數(shù)資料

| 型號(hào): | PDI1394L21BP |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 1394 full duplex AV link layer controller |

| 中文描述: | 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP100 |

| 封裝: | 14 X 14 MM, 1 MM HEIGHT, PLASTIC, SOT-386-1, TQFP-100 |

| 文件頁(yè)數(shù): | 10/42頁(yè) |

| 文件大?。?/td> | 233K |

| 代理商: | PDI1394L21BP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)

Philips Semiconductors

Preliminary data

PDI1394P23

2-port/1-port 400 Mbps physical layer interface

2001 Sep 06

10

The LPS input is considered inactive if it remains low for more than

2.6

μ

s and is considered active otherwise. When the PDI1394P23

detects that LPS is inactive, it will place the PHY-LLC interface into a

low-power reset state in which the CTL and D outputs are held in the

logic zero state and the LREQ input is ignored; however, the

SYSCLK output remains active. If the LPS input remains low for

more than 26

μ

s, the PHY–LLC interface is put into a low-power

disabled state in which the SYSCLK output is also held inactive. The

PHY-LLC interface is also held in the disabled state during hardware

reset. The PDI1394P23 will continue the necessary repeater

functions required for normal network operation regardless of the

state of the PHY-LLC interface. When the interface is in the reset or

disabled state and LPS is again observed active, the PHY will

initialize the interface and return it to normal operation.

The PHY uses the C/LKON terminal to notify the LLC to power up

and become active. When activated, the C/LKON signal is a square

wave of approximately 163 ns period. The PHY activates the

C/LKON output when the LLC is inactive and a wake-up event

occurs. The LLC is considered inactive when either the LPS input is

inactive, as described above, or the LCtrI bit is cleared to 0. A

wake-up event occurs when a link-on PHY packet addressed to this

node is received, or conditionally when a PHY interrupt occurs. The

PHY deasserts the C/LKON output when the LLC becomes active

(both LPS active and the LCtrl bit set to 1). The PHY also deasserts

the C/LKON output when a bus-reset occurs unless a PHY interrupt

condition exists which would otherwise cause C/LKON to be active.

8.0

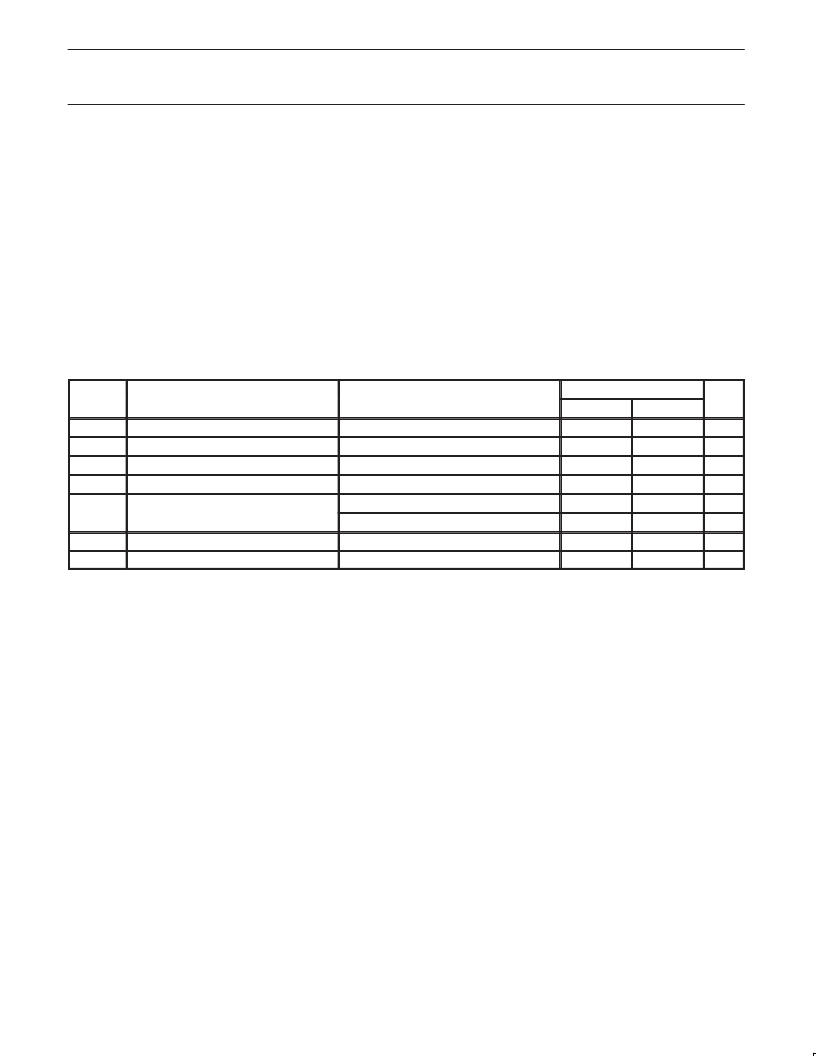

In accordance with the Absolute Maximum Rating System (IEC 134). Voltages are referenced to GND (ground = 0 V).

ABSOLUTE MAXIMUM RATINGS

1

SYMBOL

PARAMETER

CONDITION

LIMITS

UNIT

MIN

MAX

V

DD

V

I

V

I

–5V

V

O

DC supply voltage

–0.5

4.0

V

DC input voltage

–0.5

V

DD

+0.5

5.5

V

5 volt tolerant input voltage range

–0.5

V

DC output voltage range at any output

–0.5

V

DD

+0.5

2

V

Electrostatic discharge

Human Body Model

—

kV

Machine Model

—

200

V

T

amb

T

stg

Operating free-air temperature range

0

+70

°

C

°

C

Storage temperature range

–65

+150

NOTE:

1. Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under “Recommended Operating

Conditions” is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PDL-TTL-7-1 | Programmable Delay Line |

| PDL-TTL-7-14 | Programmable Delay Line |

| PDL-TTL-7-15 | Programmable Delay Line |

| PDL-TTL-7-2 | Programmable Delay Line |

| PDL-TTL-7-20 | Programmable Delay Line |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PDI1394L40 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:1394 enhanced AV link layer controller |

| PDI1394L40BE | 制造商:NXP Semiconductors 功能描述:1 CHANNEL(S), 400M BPS, SERIAL COMM CONTROLLER, PQFP144 |

| PDI1394L40BE,518 | 功能描述:視頻 IC 1394 A/V LINK LAYER RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| PDI1394L40BE,551 | 制造商:NXP Semiconductors 功能描述:1394 A/V LINK LAYER - Trays |

| PDI1394L40BE,557 | 功能描述:視頻 IC DO NOT USE ORDER -S OR -T PART RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。