- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367738 > P87C554 (NXP Semiconductors N.V.) 80C51 8-bit microcontroller(80C51 8位微控制器) PDF資料下載

參數(shù)資料

| 型號: | P87C554 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | 80C51 8-bit microcontroller(80C51 8位微控制器) |

| 中文描述: | 80C51的8位微控制器(80C51的8位微控制器) |

| 文件頁數(shù): | 29/78頁 |

| 文件大小: | 393K |

| 代理商: | P87C554 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁

Philips Semiconductors

Preliminary specification

80C554/83C554/87C554

80C51 8-bit microcontroller

16K/512 OTP/ROM/ROMless, 8 channel 10 bit A/D, I

2

C, PWM,

capture/compare, high I/O

1999 Apr 07

29

Interrupts

The 8XC554 has fifteen interrupt sources, each of which can be

assigned one of four priority levels. The five interrupt sources

common to the 80C51 are the external interrupts (INT0 and INT1),

the timer 0 and timer 1 interrupts (IT0 and IT1), and the serial I/O

interrupt (RI or TI). In the 8XC554, the standard serial interrupt is

called SIO0.

The eight Timer T2 interrupts are generated by flags CTI0-CT13,

CMI0-CMI2, and by the logical OR of flags T2OV and T2BO. Flags

CTI0 to CT13 are set by input signals CT0I to CT3i. Flags CMI0 to

CMI2 are set when a match occurs between Timer T2 and the

compare registers CM0, CM1, and CM2. When an 8-bit or 16-bit

overflow occurs, flags T2BO and T2OV are set, respectively. These

nine flags are not cleared by hardware and must be reset by

software to avoid recurring interrupts.

The ADC interrupt is generated by the ADCI flag in the ADC control

register (ADCON). This flag is set when an ADC conversion result is

ready to be read. ADCI is not cleared by hardware and must be

reset by software to avoid recurring interrupts.

The SIO1 (I

2

C) interrupt is generated by the SI flag in the SIO1

control register (S1CON). This flag is set when S1STA is loaded

with a valid status code.

The ADCI flag may be reset by software. It cannot be set by

software. All other flags that generate interrupts may be set or

cleared by software, and the effect is the same as setting or

resetting the flags by hardware. Thus, interrupts may be generated

by software and pending interrupts can be canceled by software.

Interrupt Enable Registers:

Each interrupt source can be

individually enabled or disabled by setting or clearing a bit in the

interrupt enable special function registers IEN0 and IEN1. All

interrupt sources can also be globally enabled or disabled by setting

or clearing bit EA in IEN0. The interrupt enable registers are

described in Figures 27 and 28.

There are 3 SFRs associated with each of the four-level interrupts.

They are the IENx, IPx, and IPxH. (See Figures 29, 30, and 31.) The

IPxH (Interrupt Priority High) register makes the four-level interrupt

structure possible.

The function of the IPxH SFR is simple and when combined with the

IPx SFR determines the priority of each interrupt. The priority of

each interrupt is determined as shown in the following table:

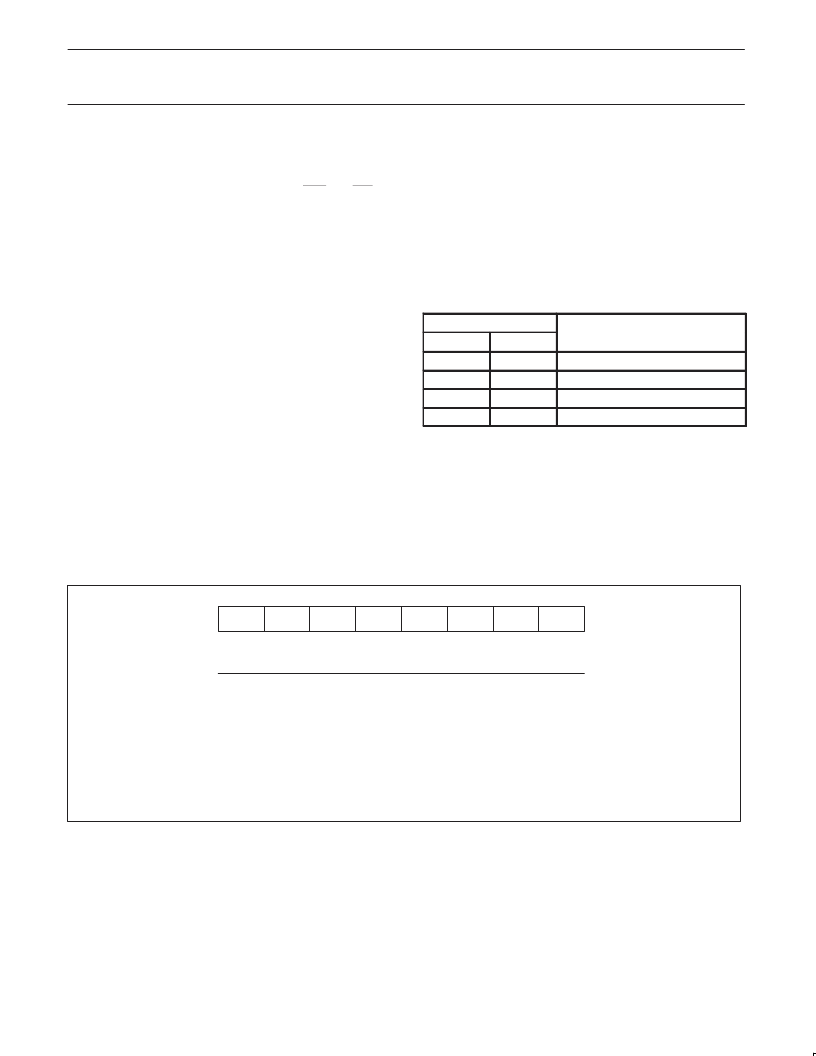

PRIORITY BITS

INTERRUPT PRIORITY LEVEL

IPxH.x

IPx.x

0

0

Level 0 (lowest priority)

0

1

Level 1

1

0

Level 2

1

1

Level 3 (highest priority)

The priority scheme for servicing the interrupts is the same as that

for the 80C51, except there are four interrupt levels rather than two

as on the 80C51. An interrupt will be serviced as long as an interrupt

of equal or higher priority is not already being serviced. If an

interrupt of equal or higher level priority is being serviced, the new

interrupt will wait until it is finished before being serviced. If a lower

priority level interrupt is being serviced, it will be stopped and the

new interrupt serviced. When the new interrupt is finished, the lower

priority level interrupt that was stopped will be completed.

EX0

BIT

SYMBOL

FUNCTION

IEN0.7

EA

Global enable/disable control

0 = No interrupt is enabled

1 = Any individually enabled interrupt will be accepted

Eanble ADC interrupt

Enable SIO1 (I

2

C) interrupt

Enable SIO0 (UART) interrupt

Enable Timer 1 interrupt

Enable External interrupt 1

Enable Timer 0 interrupt

Enable External interrupt 0

IEN0.6

IEN0.5

IEN0.4

IEN0.3

IEN0.2

IEN0.1

IEN0.0

EAD

ES1

ES0

ET1

EX1

ET0

EX0

SU00762

ET0

EX1

ET1

ES0

ES1

EAD

EA

0

1

2

3

4

5

6

7

(LSB)

(MSB)

IEN0 (A8H)

Figure 27. Interrupt Enable Register (IEN0)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P87C654X2 | Octal Edge-Triggered D-Type Flip-Flops with 3-State Outputs 20-CDIP -55 to 125 |

| P83C654X2 | 80C51 8-bit microcontroller family 16 kB OTP/ROM, 256B RAM, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz) |

| P83C654EFP | CONN HEADER 11POS SGL PCB 30GOLD |

| P83C654EFPN | CONN HEADER 13POS SGL PCB 30GOLD |

| P83C654EHA | CMOS single-chip 8-bit microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P87C554SBAA | 制造商:NXP Semiconductors 功能描述:MCU 8-Bit 87C 80C51 CISC 16KB EPROM 5V 68-Pin PLCC |

| P87C554SBAA,512 | 功能描述:8位微控制器 -MCU 80C51 16K/512 OTP RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| P87C554SBBD | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:80C51 8-bit microcontroller . 6 clock operation 16K/512 OTP/ROM/ROMless, 7 channel 10 bit A/D, I2C, PWM, capture/compare, high I/O, 64L LQFP |

| P87C554SFAA | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:80C51 8-bit microcontroller ? 12 clock operation 16K/512 OTP/RAM 8 channel 10-bit A/D, I2C, PWM, capture/compare, high I/O |

| P87C554SFAA,512 | 功能描述:8位微控制器 -MCU 80C51 16K/512 OTP RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。