- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄359233 > MT8930C (Zarlink Semiconductor Inc.) Subscriber Network Interface Circuit PDF資料下載

參數(shù)資料

| 型號(hào): | MT8930C |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | Subscriber Network Interface Circuit |

| 中文描述: | 用戶網(wǎng)絡(luò)接口電路 |

| 文件頁(yè)數(shù): | 4/41頁(yè) |

| 文件大小: | 2516K |

| 代理商: | MT8930C |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)

MT8930C

Data Sheet

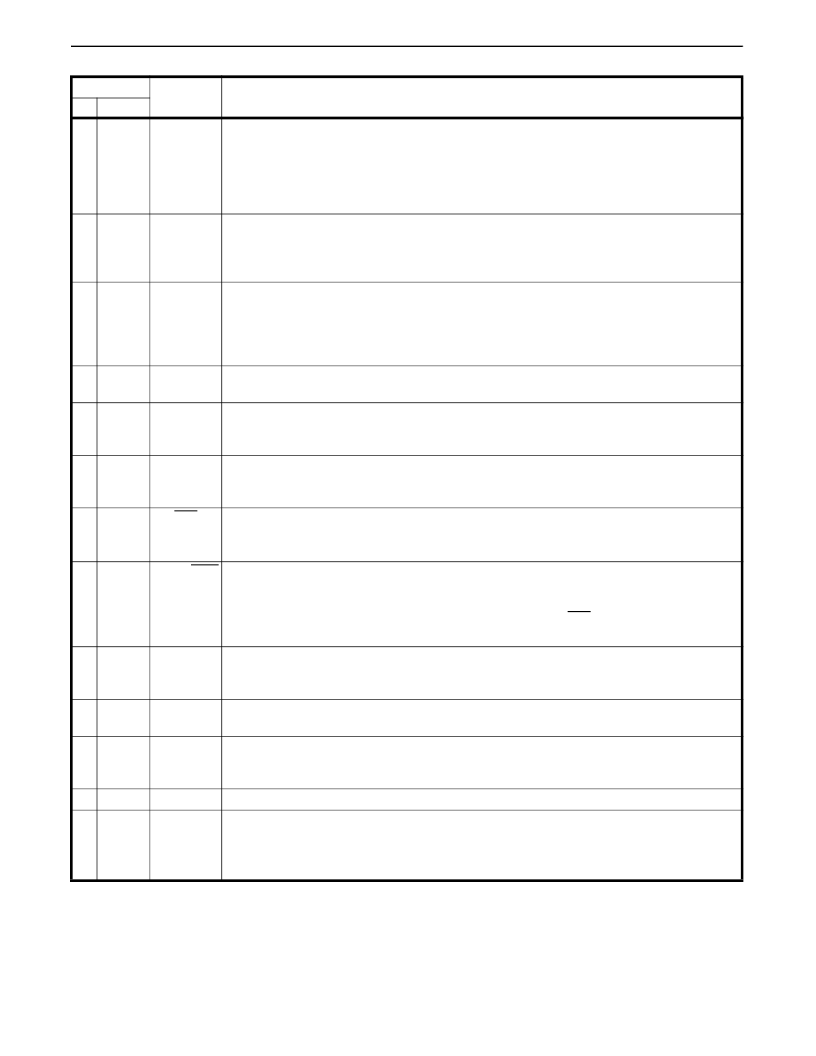

4

17

26

SYNC/BA

Synchronization/Bus Activity Output (Cmode = 0):

output indicating synchronization

to incoming RX frames when activation request is asserted and the deactivation request

is ’0’ (AR = 1 and DR = 0). Synchronization is declared once three successive frames

conforming to the 14-bit bipolar violation criteria have been detected. If part is

deactivated or activation request is ’0’ (AR = 0 or DR = 1), this pin indicates the

presence of bus activity.

MFR

Multiframe Input/Output (Cmode=0):

multiframe input in NT mode or output in TE

mode. Setting this pin to one in NT mode when HALF = 1, forces the F

A

, N pair to 1, 0

respectively. This pin going high in TE mode indicates that F

A

= 1 & N= 0 has been

received. This signal is updated on the rising edge of the HALF signal.

MCH

Maintenance Channel (Q-channel) Input/Output (Cmode=0):

an output in NT mode

which is valid only in the frame following the transmission of MFR. In TE mode, this is

the maintenance channel (Q-channel) input which is transmitted in the F

A

and L bits

following the reception of the multiframe signal. This input is sampled on the falling

edge of the HALF signal.

M/S

M/S Input/Output (Cmode=0):

M/S bit input in NT mode or M/S bit output in TE mode.

M is read or written when HALF=1 while S is read or written when HALF=0.

AR

Activate Request Input (Cmode = 0):

asserting AR with DR = 0 will initiate the

appropriate S-interface activation sequence coded in the NT or TE activation/

deactivation controller.

DR

Deactivate Request Input (Cmode = 0):

asserting DR high will initiate the appropriate

S-interface deactivation sequence coded in the NT or TE activation/ deactivation

controller.

18

30

19

31

20

32

21

34

22

35

23

37

Rsti

Reset Input:

Schmitt trigger reset input. If ’0’, sets all control registers to the default

conditions, resets activation state machines to the deactivated state, resets HDLC,

clears the HDLC FIFO‘s. Sets the microport to Motorola bus mode.

24

38

STAR/Rsto

Star/Reset (Open Drain Output):

192kbit/s Rx data output fixed relative to the ST-BUS

timebase. A group of NTs, in fixed timing mode, can be wire or’ed together to create a

Star configuration. Active low reset output in TE mode indicating 128 consecutive

marks have been received. Can be connected directly to

Rsti to allow NT to reset all

TEs on the bus. This pin must be tied to V

DD

with a 10 k

resistor.

LRx

Receive Line Signal Input:

this is a high impedance input for the pseudoternary line

signal to be connected to the line through a 2:1 ratio transformer. See Figures 20 and

21. A DC bias level on this input equal to V

Bias

must be maintained.

LTx

Transmit Line Signal Output:

this is a current source output designed to drive a

nominal 50 ohm line through a 2:1 ratio transformer. See Figures 20 and 21.

V

Bias

Bias Voltage:

analog ground for Tx and Rx transformers. This pin must be decoupled

to V

DD

through a 10

μ

F capacitor with good high frequency characteristics (i.e.,

tantalum).

V

DD

Power Supply Input.

NC

No Connection.

25

40

26

42

27

43

28

44

1,5-6,10-

12,15,18,

23,27-29,

33, 36,

39, 41

Pin Description (continued)

Pin #

Name

Description

DIP

PLCC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT8930CE | Subscriber Network Interface Circuit |

| MT8930CP | Subscriber Network Interface Circuit |

| MT8931C | Subscriber Network Interface Circuit |

| MT8931CE | Subscriber Network Interface Circuit |

| MT8931CP | Subscriber Network Interface Circuit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT8930C-1 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit |

| MT8930CC | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit Preliminary Information |

| MT8930CE | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Subscriber Network Interface Circuit |

| MT8930CP | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Subscriber Network Interface Circuit |

| MT8930CPR | 制造商:Microsemi Corporation 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。