- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45354 > MPC8241LZQ266B (MOTOROLA INC) 32-BIT, 266 MHz, RISC PROCESSOR, PBGA357 PDF資料下載

參數(shù)資料

| 型號: | MPC8241LZQ266B |

| 廠商: | MOTOROLA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 266 MHz, RISC PROCESSOR, PBGA357 |

| 封裝: | 25 X 25 MM, 1.27 MM HEIGHT, PLASTIC, BGA-357 |

| 文件頁數(shù): | 18/60頁 |

| 文件大?。?/td> | 730K |

| 代理商: | MPC8241LZQ266B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

MOTOROLA

MPC8241 Integrated Processor Hardware Specifications

25

Electrical and Thermal Characteristics

1.4.3.4

I2C AC Timing Specifications

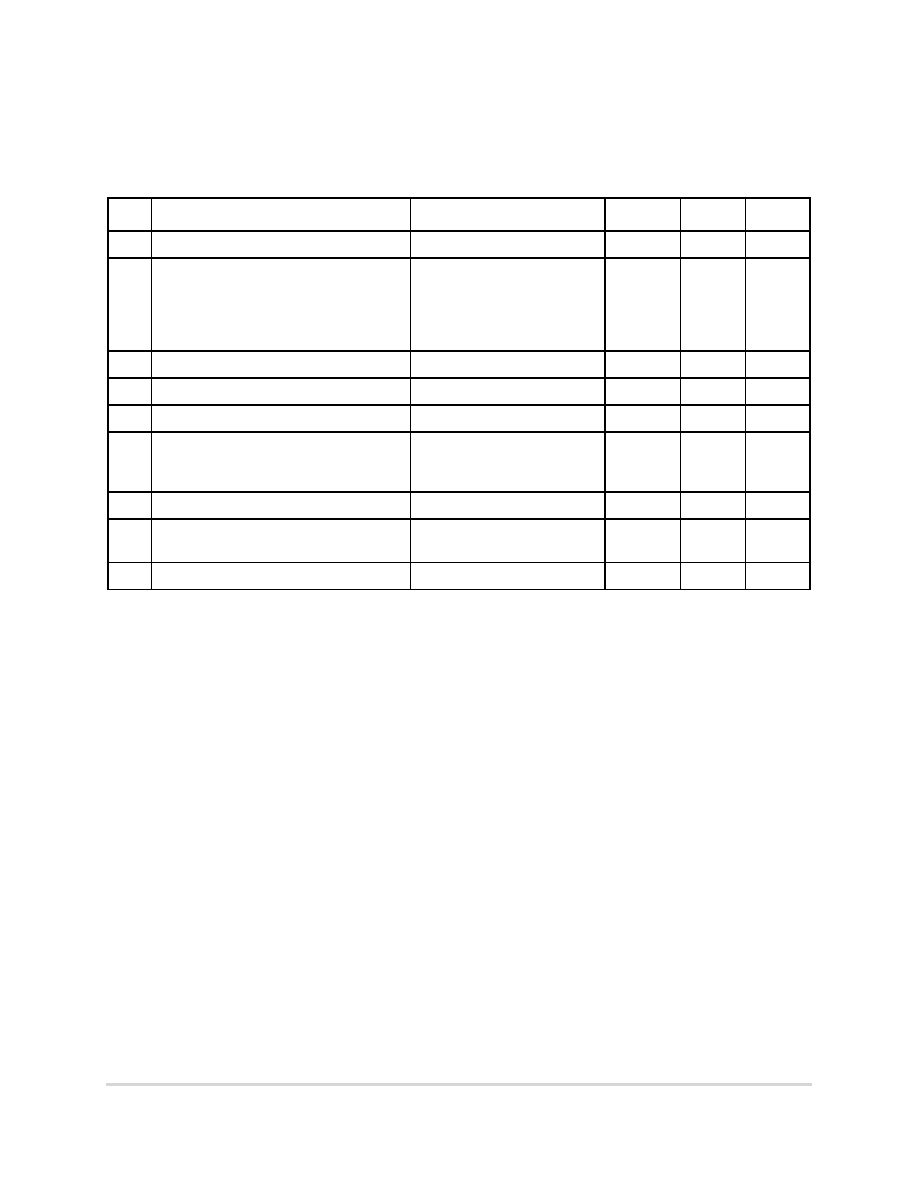

Table 12. I2C Input AC Timing Specifications

Num

Characteristic

Min

Max

Unit

Notes

1

Start condition hold time

4.0

—

CLKs

1, 2

2

Clock low period

(time before the MPC8241 will drive SCL

low as a transmitting slave after detecting

SCL low as driven by an external master)

8.0 + (16

× 2FDR[4:2]) × (5 –

4({FDR[5],FDR[1]} == b’10) –

3({FDR[5],FDR[1]} == b’11) –

2({FDR[5],FDR[1]} == b’00) –

1({FDR[5],FDR[1]} == b’01))

—

CLKs

1, 2, 4, 5

3

SCL/SDA rise time (from 0.5 to 2.4 V)

—

1

ms

4

Data hold time

0

—

ns

2

5

SCL/SDA fall time (from 2.4 to 0.5 V)

—

1

ms

6

Clock high period (time needed to either

receive a data bit or generate a START or

STOP)

5.0

—

CLKs

1, 2, 5

7

Data setup time

3.0

—

ns

3

8

Start condition setup time (for repeated

start condition only)

4.0

—

CLKs

1,2

9

Stop condition setup time

4.0

—

CLKs

1, 2

Notes:

1. Units for these specifications are in SDRAM_CLK units.

2. The actual values depend on the setting of the digital filter frequency sampling rate (DFFSR) bits in the frequency

divider register I2CFDR. Therefore, the noted timings in the above table are all relative to qualified signals. The

qualified SCL and SDA are delayed signals from what is seen in real time on the I2C bus. The qualified SCL, SDA

signals are delayed by the SDRAM_CLK clock times DFFSR times two plus one SDRAM_CLK clock. The resulting

delay value is added to the value in the table (where this note is referenced). See Figure 17.

3. Timing is relative to the sampling clock (not SCL).

4. FDR[x] refers to the frequency divider register I2CFDR bit x.

5. Input clock low and high periods in combination with the FDR value in the frequency divider register (I2CFDR)

相關PDF資料 |

PDF描述 |

|---|---|

| MPC8241LVR200B | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA357 |

| MPC8245ARZU400D | 32-BIT, 400 MHz, RISC PROCESSOR, PBGA352 |

| MPC8245ARZU466D | 32-BIT, 466 MHz, MICROPROCESSOR, PBGA352 |

| MPC8245LVV333D | 32-BIT, 333 MHz, RISC PROCESSOR, PBGA352 |

| MPC8245LVV350D | 32-BIT, 350 MHz, RISC PROCESSOR, PBGA352 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MPC8241LZQ266D | 功能描述:微處理器 - MPU 266MHz 266MIPS RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8241TVR166D | 功能描述:微處理器 - MPU INTEGRATED HOST PROC RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8241TVR200D | 功能描述:微處理器 - MPU INTEGRATED HOST PROC RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8241TZP166C | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Intergrated Processor Hardware Specifications |

| MPC8241TZP200C | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Intergrated Processor Hardware Specifications |

發(fā)布緊急采購,3分鐘左右您將得到回復。